一种利用混合补偿的低功耗环形振荡器设计实现

振荡器是现代电路系统中不可缺少的一部分,在无线通讯、计算、信号处理等领域应用广泛。晶体振荡器具有较高的精度和较好的频率质量,但无法集成到SoC系统中去,需留有外接时钟信号接口,增大了系统体积和功耗。随着可穿戴设备、可植入设备的发展,越来越需要低功耗、面积小、可集成的片上时钟系统,环形振荡器可满足以上要求,是较为理想的片上时钟候选技术。但是其频率的稳定性却受温度、电压、工艺的影响较大,因此如果能够解决环形振荡器的频率稳定性问题,将具有重要的研究意义。

表 1 振荡器在不同领域中的应用举例

| 应用 | 振荡器的作用 |

| FDMA | 调谐频率,下变频 |

| 蓝牙发射机 | 调谐频率,上变频 |

| FM射频前端 | 调谐频率,下变频 |

| 卫星调谐器 | 调谐频率,下变频 |

| 卫星LNB | 混合频率,下变频 |

| 基带数字处理 | 产生时钟 |

| 手表 | 计时参考 |

| FM射频解调器 | 解调 |

| 光学发射机 | 时钟产生和变换 |

| 光接收机 | 载波再生 |

| 加速度传感器 | 压力检测 |

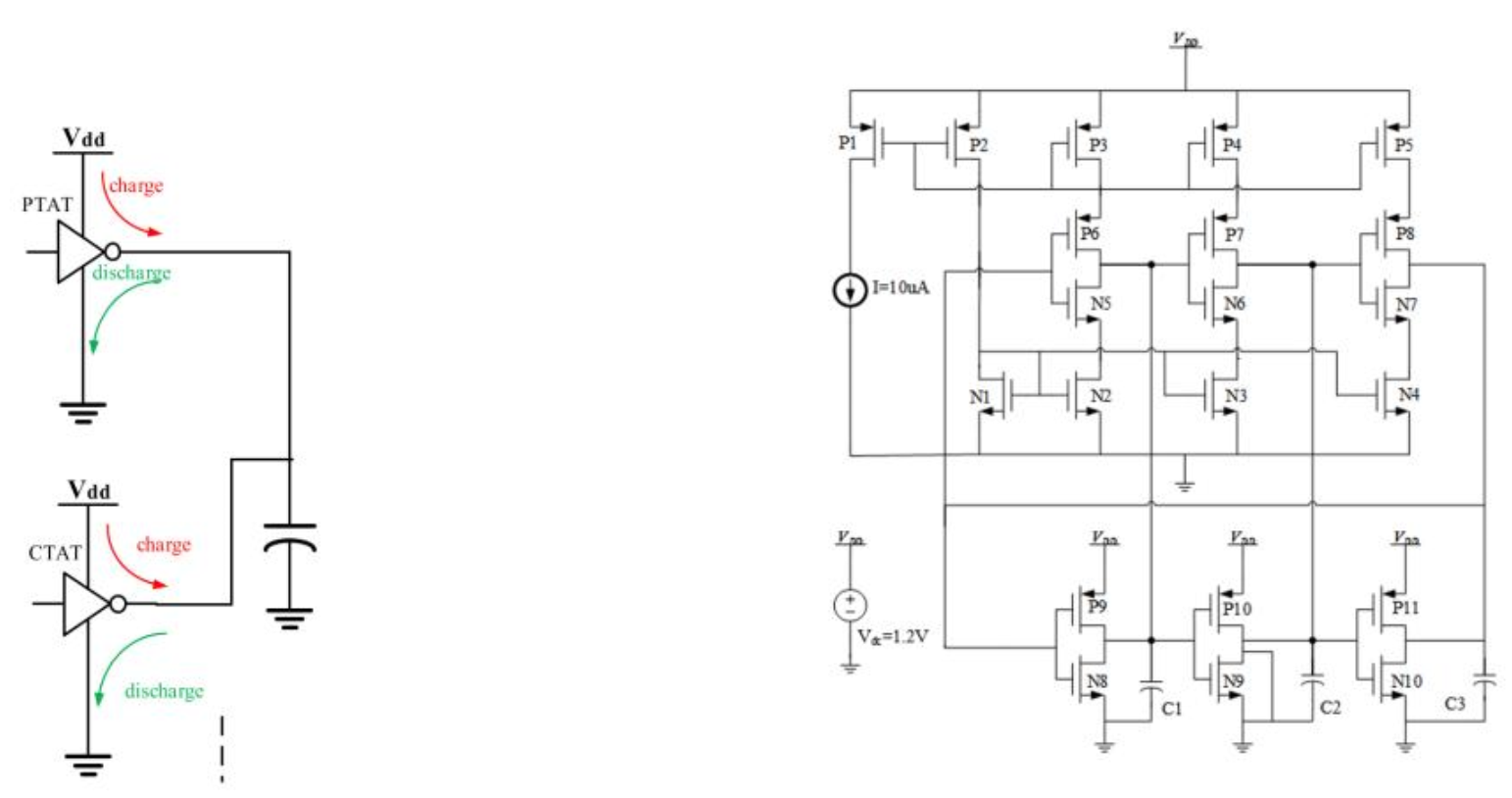

对环形振荡器频率补偿的设计一般采用外围电路补偿基本振荡单元的频率漂移,但这增加了系统的功耗和面积,对频率的补偿也存在固有的极限。北京大学集成微系统实验室王瑞同学从新的角度出发,利用相反温度特性的延迟单元对环形振荡器的频率进行抵消补偿,提出了并联混合补偿方式和混合延迟单元设计两种思路,并设计了一种新的延迟单元。同时提出了高阶消除和低阶消除的补偿思想,利用混合环形振荡器验证了两种方式的正确性,出于需要还设计了一种具有与温度呈线性关系的电压电路,此电路的输出电压只与器件的参数比值有关。

图 1 两单元混合并联环形振荡器原理图

图 2 两单元混合并联环形振荡器版图

基于SMIC 130nm工艺,对两单元混合并联环形振荡器进行了版图设计与验证,结果表明具有很好的频率稳定性,当温度由-40℃ 变到125℃ 时,振荡器的输出频率在9.287MHz到9.299MHz之间波动,变化了仅0.13%。温度漂移为7.83ppm/℃。由于采用了倒比管的Cascode结构,因此对电源电压波动具有一定抑制作用,当电源电压从1V变化到3.24V时,频率从9.05MHz变化到9.28MHz,变化只有0.99%/V,因此具有较好的电压抑制能力。与其他最新的补偿方式相比,由于引入了倒比管获得了更小的功耗,进而也降低了负载电容的大小,使其面积也进一步降低,新的延迟单元使用晶体管更少,结构更加简单,系统稳定性更高。

表 2 性能对比

| 本文 | JSSC2006 | EL2007 | MWSCAS2018 | JSSC2016 | |

| 工艺[nm] | 130 | 250 | 180 | 130 | 180 |

| 电源电压[V] | 1.2 | 2.5 | 1.2 | 1.2 | 3 |

| 频率[Hz] | 9.288M | 7.03M | 70400 | 13.4M | 1.9M |

| 温度变化范围[℃] | -40-125 | -40-125 | -40-80 | -40-80 | -40-85 |

| 温度波动[%] | 0.13 | 士0.84 | 0.416 | 0.175 | 1.16 |

| 温度漂移[ppm/℃] | 7.83 | 50.9 | 34.3 | 14.6 | 92.8 |

| 工艺波动 | 1.48% | 士1.1% | N/A | 1.19% | 士2.5% |

| 电源电压波动[%/V] | 0.99

(1V-3.2V) |

士0.31

(2.4V-2.75V) |

0.75 | 0.06 | 0.044

(3V-3.6V) |

| 功耗 | 14.4uW | 1.5mW | 110nW | 584uW | 390uW |

| 面积[mm ] | 0.0014 | 0.26 | 0.0858 | 0.22 |