全数字锁相环中高线性度DTC的设计与实现

全数字锁相环在无线系统应用领域中的主要障碍是其较高的输出杂散,该杂散的水平主要由时间数字转换器(TDC)的非线性和其有限的分辨率决定。由于TDC的设计难度大,校准技术过于复杂,数字时间转换器(DTC)辅助TDC结构的ADPLL应运而生,该结构缓解了TDC的设计压力,减小了TDC的鉴相范围,有很好的前景。可惜的是,虽然DTC的结构简单,但是DTC的积分非线性误差(INL)同样会给整个系统引入杂散,因此设计一个高精度、高线性度的DTC结构已经成为必然。

为降低电路的非线性,需要设计一个高精度、高线性度的10bitDTC结构。作者设计了一种简单的方法实现了充电斜率的近似恒定。与此同时,为减小二进制编码方式带来的非线性问题,作者使用了分段的编码方式对电容阵列进行控制。

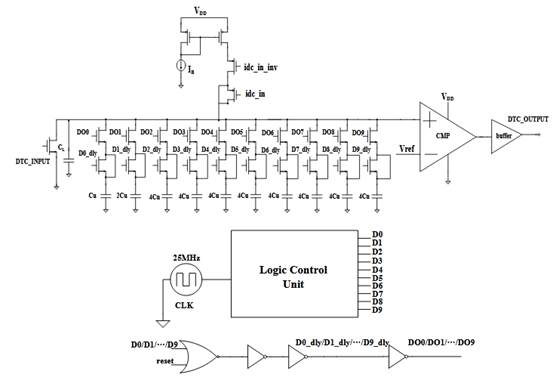

设计的10bitDTC电路结构如图1所示,电路总体包含了以下七个部分:电流镜、数字逻辑控制单元、电容阵列和与之对应的MOS开关阵列、一个由输入信号DTC_INPUT控制的NMOS开关,基于开环运放的电压比较器、电压基准电路以及输入/输出缓冲器。

图1 10 bit DTC电路结构

电路的工作原理如下:当DTC_INPUT信号为0时,由于DTC_INPUT控制一个NMOS开关,因此该开关断开,此时电流镜开关和电容阵列中的控制开关被打开,电容阵列开始充电,当充电至比较器的翻转电压refV时,比较器翻转;当DTC_INPUT信号为1时,由DTC_INPUT控制的NMOS开关管被打开,此时电流镜关闭,电容上的充电电荷通过该NMOS开关管进行泄放。该过程具有周期性,相邻两个周期之间会有一个固定的时间差,该固定时间差即为DTC的精度。整体版图如图2所示

图2 DTC整体版图

基于SMIC 130nm的工艺,在Cadence平台下,该DTC的精度为315fs,INL为0.52LSB,功耗为26.4uW。