ADPLL中DTC的杂散建模与可综合电路实现

微电子工艺的进步使电路的电压范围压缩变小而时间边沿却越来越陡峭精准。因此工作在时间域的全数字锁相环逐步替代模拟电压域锁相环。全数字锁相环中的TDC(Time to digital converter)对线性度、动态范围和精度要求严苛,为了缓解设计压力,人们引入了DTC(Digital to time converter)来辅助TDC,因而DTC成为全数字锁相环中的重要模块。

针对目前已有论文的DTC非线性导致锁相环的分数杂散的计算结果与仿真结果有较大出入这一问题,提出了一种预测DTC的非线性导致的杂散的方法。该方法改进了比较器输入信号斜率与比较器本身传播延时的关系。本推导方法对于形状近似于正弦/余弦的DTC的INL,比已有方法精确大约2dBc,对于形状不是正弦/余弦的DTC的INL,即已有方式无法推导的情况,最差情况误差约为2dBc。

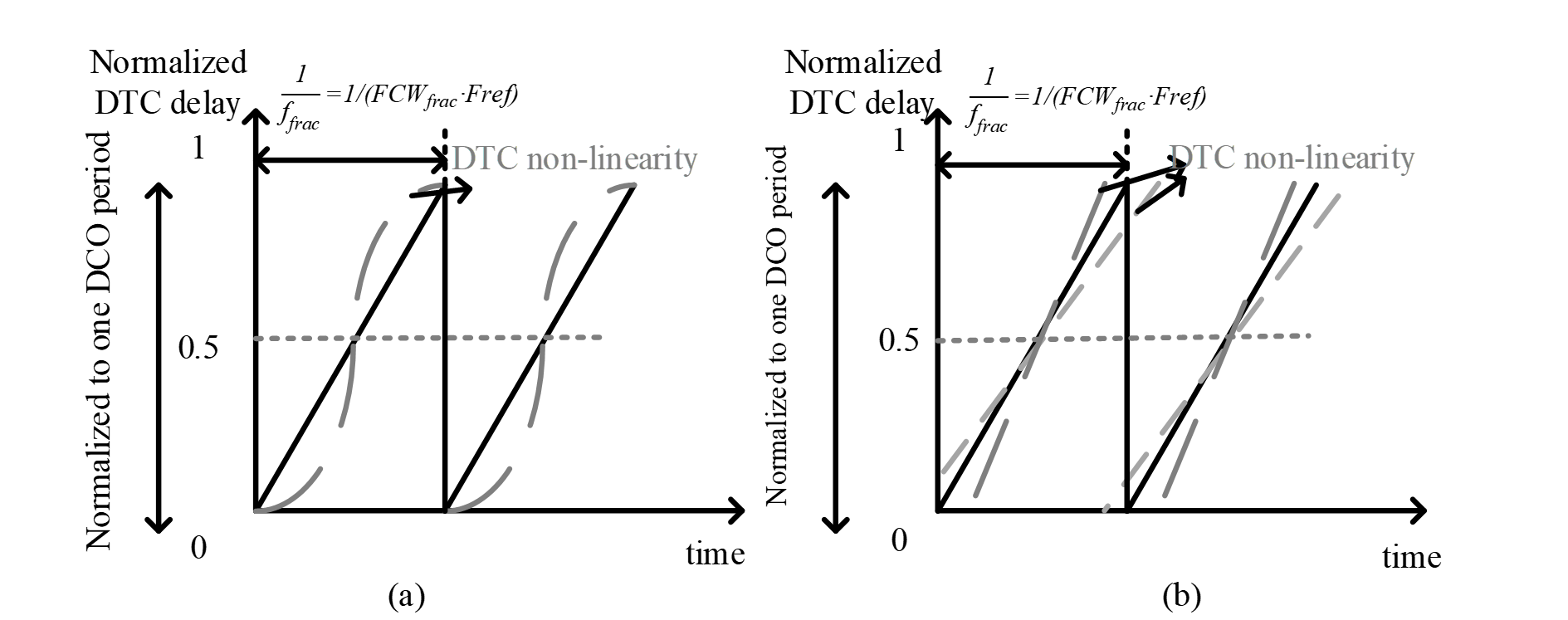

图3.6 DTC非线性形状(a)正弦/余弦形状(b)非正弦/余弦形状

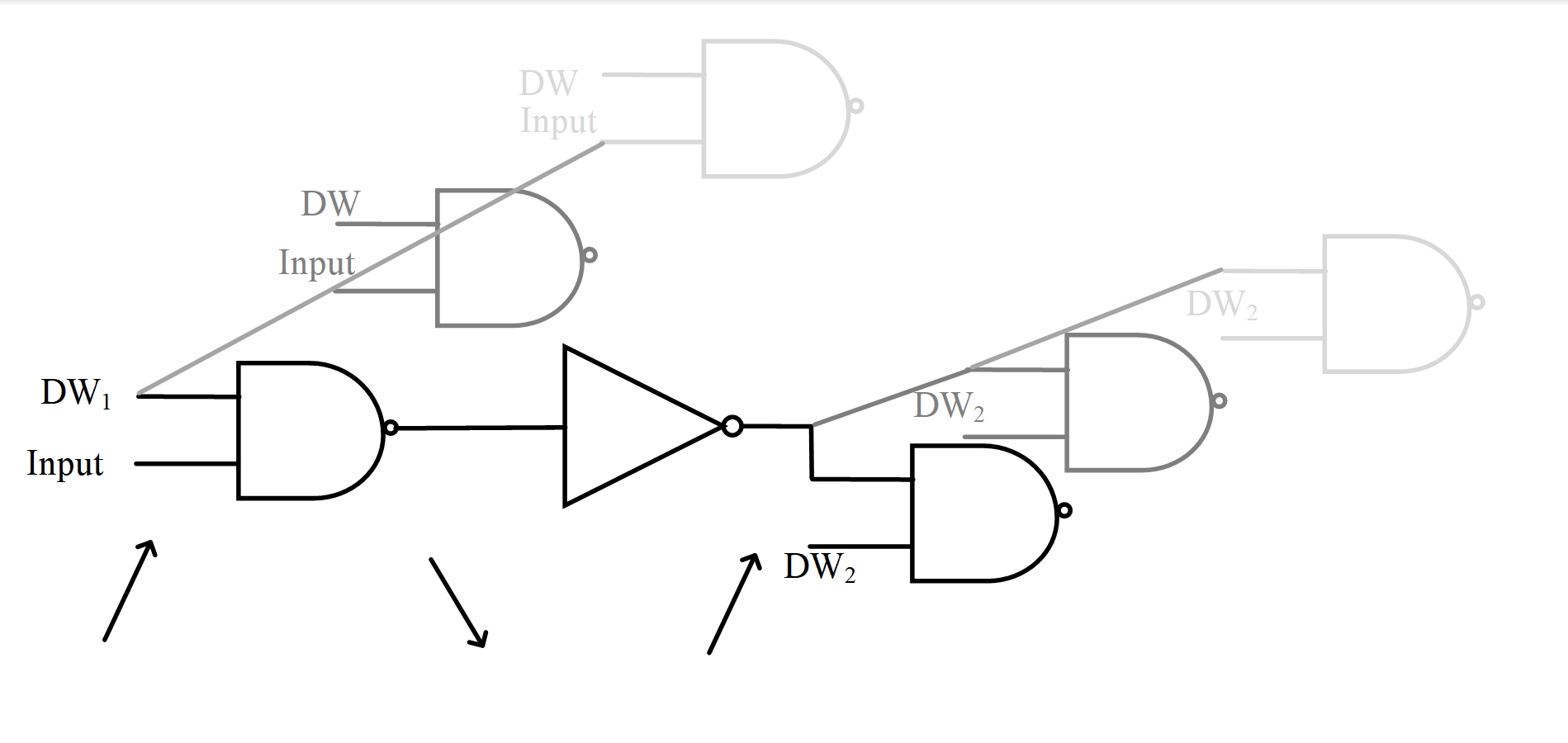

针对目前大部分DTC仍用手工版图设计这一问题,提出一种用数字单元电路实现高线性度的、可自动综合的DTC。其利用了“当比较器延时较大时,该比较器的负载电容值会减小,令传播延时变小”这二者效应的叠加,即可抵消大部分失配,实现高线性度。后仿结果表明该DTC的最大DNL为-0.12LSB,最大INL为-1.1LSB。

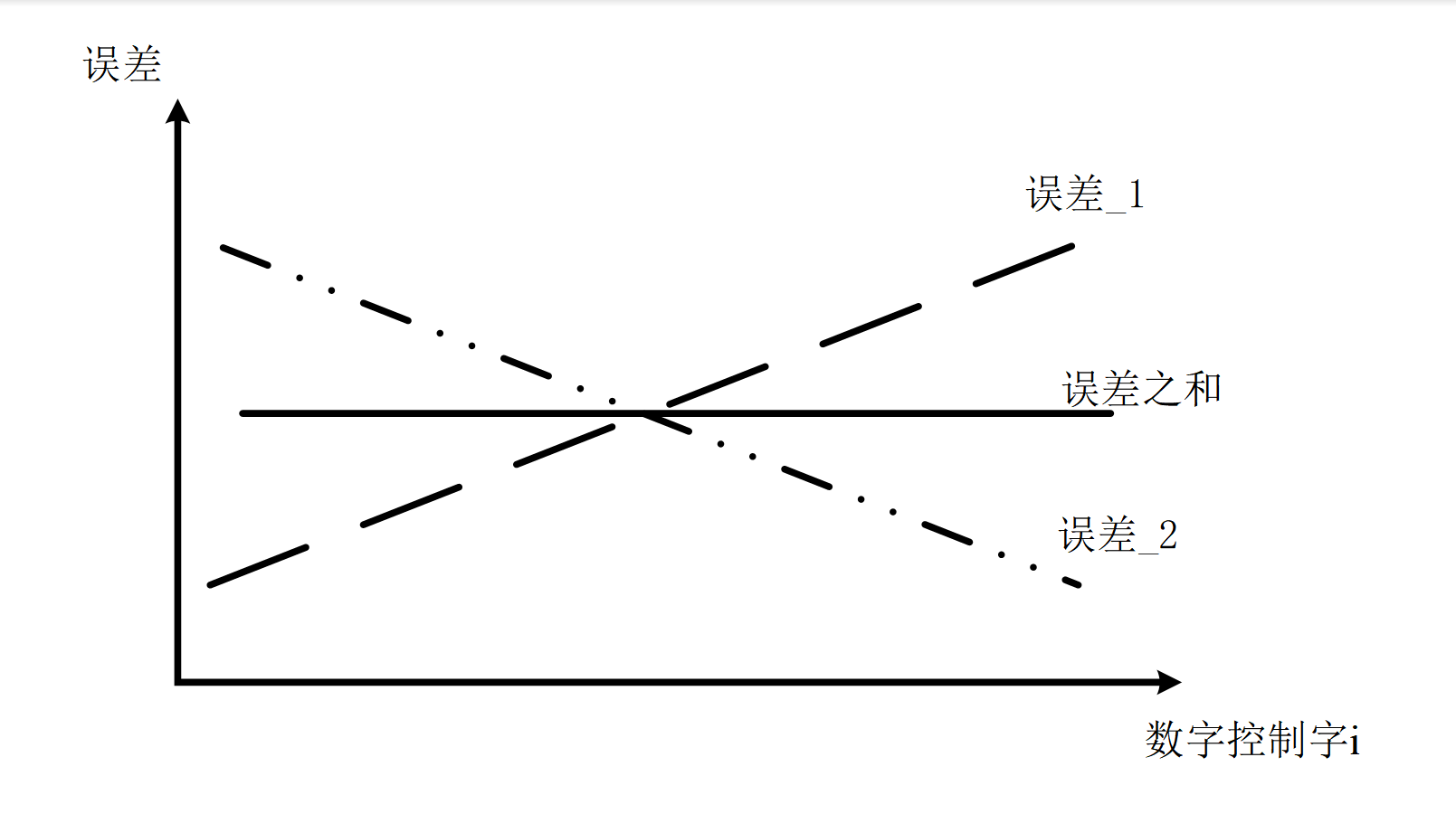

图4.5 误差相加相消原理

图4.6 高线性可综合DTC原理图