北京大學

# 博士研究生学位论文

题目： 多晶硅薄膜晶体管 KINK 和离散晶界效应及面板无畸变传输线研究

姓 名： 刘驰

学 号： 1001110936

院 系： 信息科学技术学院

专 业： 微电子学与固体电子学

研究方向： ULSI 新器件及集成技术

导师姓名： 张盛东

二〇一三年六月

# 版权声明

任何收存和保管本论文各种版本的单位和个人，未经本论文作者同意，不得将本论文转借他人，亦不得随意复制、抄录、拍照或以任何方式传播。否则，引起有碍作者著作权之问题，将可能承担法律责任。

## 摘要

多晶硅薄膜晶体管具有高迁移率，可以实现像素矩阵和周边驱动电路的集成，从而大幅提升显示系统的性能和可靠性以及降低制造成本，因而成为高性能 LCD、OLED 等先进显示的核心技术之一。多晶硅薄膜晶体管的有源层为浮体结构，内部含有大量晶界，由此带来的 KINK 效应和离散晶界效应强烈影响器件的性能。此外，为实现大面积、高分辨率显示，改善面板的信号完整性十分必要。本论文对多晶硅薄膜晶体管的 KINK 效应和离散晶界效应进行了研究，并提出了用于改善面板信号完整性的无畸变传输线方案。

在 KINK 效应研究方面，本论文对多晶硅薄膜晶体管做了二维数值仿真，给出了非传统寄生双极晶体管电流传导机制，指出了寄生晶体管机制和碰撞电离机制的相互关联并解释了发射极电流增益随漏电压增加而下降的现象，指出 KINK 效应的机制是相互关联的非传统寄生晶体管机制和碰撞电离机制的联合机制；利用仿真结果，本论文解释了沟长对 KINK 效应的影响，与此同时，通过对薄膜晶体管和绝缘体上硅的仿真结果的对比分析，本论文还提出并解释了陷阱的存在将使得薄膜晶体管器件的 KINK 效应更容易受沟道长度影响。

在离散晶界效应研究方面，本论文提出并解释了晶界上陷阱浓度越少、晶界数目越少、晶界位置越靠近漏端，器件 KINK 效应越强；本论文还提出并解释了与晶界处碰撞电离有关的现象，即多晶硅薄膜晶体管的输出特性曲线中的大电流现象，以及在转移特性曲线中的翘曲现象，同时指出，晶界处的碰撞电离效应同样可以引起特殊的 KINK 效应；此外，本论文得到了考虑晶界位置和 DIGBL 效应的多晶硅薄膜晶体管表面势模型和势垒高度模型，模型结果简洁，可用来指导分析与 DIGBL 现象和晶界位置有关的现象，并为进一步得到考虑晶界位置影响的多晶硅薄膜晶体管传导电流模型提供了基础。

在用于面板的无畸变传输线研究方面，本论文提出了将栅极扫描线改造成无畸变传输线的原理，其输出波形的信号完整性得到显著提高；本论文还提出了利用传输线线间电容和线间电感的无畸变传输结构-LC 线，它可以实现信号的无畸变传输，并可以被应用在面板中以增强信号的完整性；此外，本论文得到了具有各种类型负载的无畸变传输线的解析模型，模型物理意义明显，精度极高，同时更具有快速、解析的优势。在这些模型的基础上，可以得到稳态电压、延迟、建立时间的解析表达式，从而可以进行无畸变传输线的调优设计。

关键词： 多晶硅薄膜晶体管，KINK 效应，晶界效应，无畸变传输线，精简模型。

# Study on KINK Effect and Discrete Grain Boundary Effect of Poly-Si TFTs and Distortionless Transmission Lines in Flat Panel Display

Tony C. Liu (Microelectronics)

Directed by Shengdong Zhang

## Abstract

The Poly-Silicon Thin Film Transistor (Poly-Si TFT) is regarded as one of most promising technologies for future flat panel displays such as LCD and OLED, since the high mobility and high drive current can enable the integration of pixels and driver circuits for the System-on-Panel technology. The unique structures of floating body and grain boundaries of Poly-Si TFTs induce KINK effect and discrete grain boundary effect while the signal integrity is very important for advanced flat panel displays with large area and high definition. In this thesis, the study of KINK effect and discrete grain boundary effect is done while distortionless transmission technologies are proposed for enhancing the signal integrity of flat panel displays.

On the study of KINK effect, using two dimensional simulation, the new current conduction mechanism of parasitic bipolar transistor is proposed, and the relationship between the parasitic transistor and impact ionization is proposed to explain the unusual phenomenon that the current gain of the parasitic transistor decreases when the drain voltage increases, indicating that the new parasitic bipolar transistor mechanism and impact ionization mechanism are linked and both contribute to the mechanism of KINK effect; Besides, based on the simulation results, the effect of channel length on KINK effect is analyzed, meanwhile, the effect of trap density is analyzed through comparison of TFT and SOI devices via simulations indicating the trap makes the KINK effect of TFT easier affected by the channel length.

On the study of discrete grain boundary effect, this thesis points out that with less trap density, few grain boundaries, and less distance between the grain boundaries and the drain end, the KINK effect will become more severe; Using the TCAD tools, the grain boundary impact ionization effects- the large current in the output characteristics and the kink in the transfer characteristics- are proposed and explained while the grain boundary impact ionization induced

KINK effect is also proposed; Meanwhile, the surface potential model and the potential barrier height model are proposed to model DIGBL effect and the effect of grain boundary locations. The model is accurate yet simple, predicting the DIGBL effect and the grain boundary location effect well, providing the basis for compact modeling of Poly-Si TFT current considering grain boundary locations.

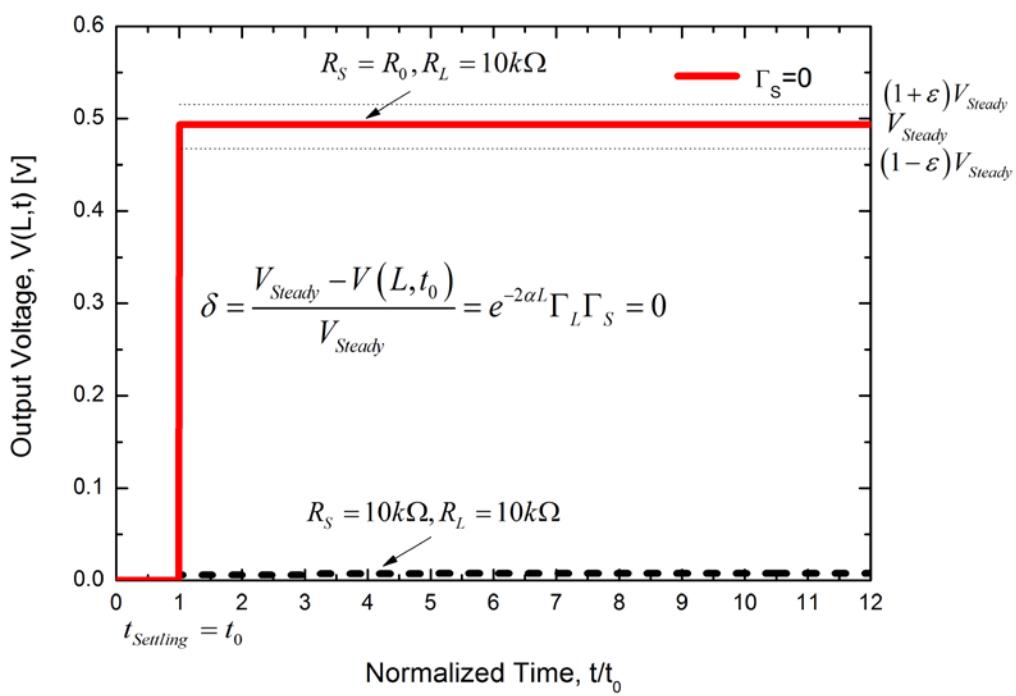

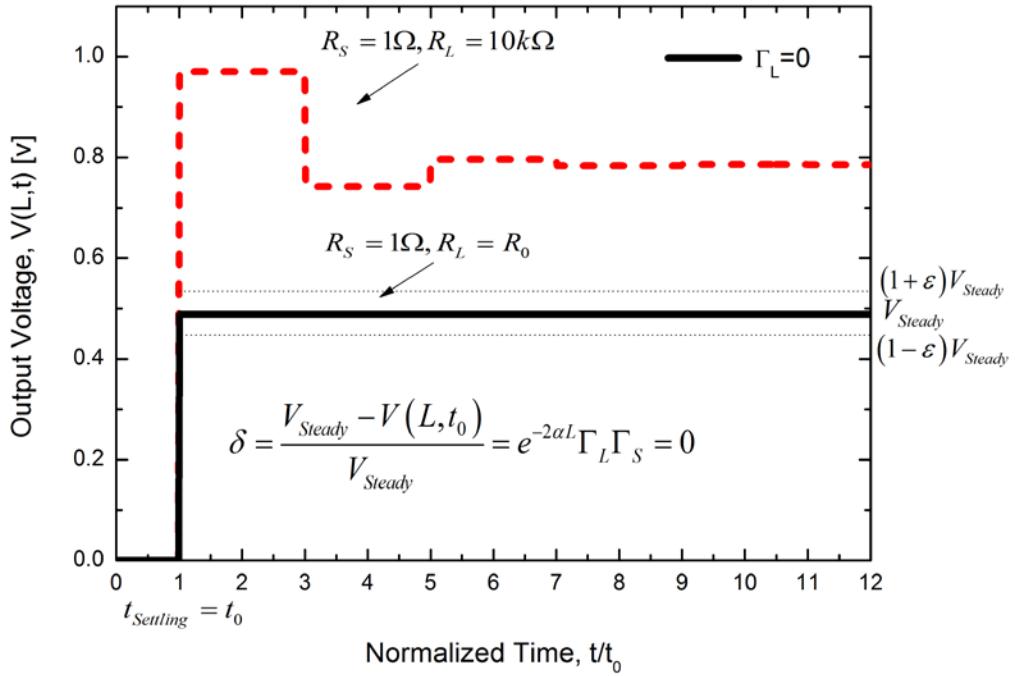

On the study of signal integrity enhancement for flat panel display, distortionless transmission technologies are proposed in this thesis. Via making the gate line a distortionless transmission line, the signal integrity of the output voltage is enhanced; Moreover, using the mutual capacitance and inductance between two transmission lines, the distortionless transmission structure-LC lines is proposed, which enables distortionless transmission and enhances signal integrity in flat panel displays; Besides, compact models for distortionless transmission lines with resistive/capacitive/inductive loads are rigorously derived with clear physical insights and high accuracy, and they can be used for deriving analytical expressions of steady-state voltage , delay time and settling time for optimized design of distortionless transmission line.

**Keywords:** Poly-Silicon Thin Film Transistor, KINK effect, Grain Boundary Effect, Distortionless Interconnect, Compact Model.

# 目录

|                                           |            |

|-------------------------------------------|------------|

| 版权声明.....                                 | I          |

| 摘要 .....                                  | II         |

| <b>Abstract.....</b>                      | <b>III</b> |

| 目录 .....                                  | V          |

| <br>                                      |            |

| 第一章 绪论.....                               | 1          |

| 1.1 多晶硅薄膜晶体管简述 .....                      | 1          |

| 1.2 本论文研究的问题 .....                        | 4          |

| 1.3 本论文的贡献和章节安排 .....                     | 7          |

| <br>                                      |            |

| 第二章 多晶硅薄膜晶体管 KINK 效应研究.....               | 10         |

| 2.1 传统 KINK 效应机制的局限性 .....                | 10         |

| 2.2 考虑非传统寄生晶体管性质的 KINK 效应机制 .....         | 20         |

| 2.2.1 多晶硅薄膜晶体管的数值仿真.....                  | 20         |

| 2.2.2 非传统寄生晶体管性质及 KINK 效应机制.....          | 29         |

| 2.2.3 寄生晶体管中的集电极电流特性分析.....               | 36         |

| 2.3 考虑寄生晶体管性质和陷阱影响的沟长对 KINK 效应的影响机制 ..... | 37         |

| 2.3.1 考虑寄生晶体管性质的沟长对 KINK 效应的影响机制.....     | 37         |

| 2.3.2 沟长对 KINK 效应影响机制中陷阱的作用 .....         | 41         |

| <br>                                      |            |

| 第三章 多晶硅薄膜晶体管离散晶界效应研究.....                 | 45         |

| 3.1 离散晶界效应简述 .....                        | 45         |

| 3.2 晶界的数目、位置及其上陷阱浓度对 KINK 效应的影响 .....     | 55         |

| 3.2.1 晶界上陷阱浓度对 KINK 效应的影响.....            | 56         |

| 3.2.2 晶界数目对 KINK 效应的影响.....               | 57         |

| 3.2.3 晶界位置对 KINK 效应的影响.....               | 57         |

| 3.3 多晶硅薄膜晶体管中的晶界处碰撞电离现象 .....             | 61         |

| 3.3.1 输出特性曲线中的大电流现象.....                  | 61         |

| 3.3.2 转移特性曲线中的翘曲现象.....                   | 64         |

| 3.3.3 晶界处碰撞电离与 KINK 效应.....               | 66         |

| 3.4 考虑 DIGBL 效应和晶界位置的晶界处势垒高度模型 .....      | 68         |

| 3.4.1 表面势模型.....                          | 68         |

| 3.4.2 势垒高度模型.....                         | 73         |

| <br>                                      |            |

| 第四章 用于面板的无畸变传输线研究.....                    | 76         |

| 4.1 面板的信号完整性问题简述 .....                    | 76         |

| 4.2 无畸变传输线简述 .....                        | 81         |

| 4.3 无畸变传输线在面板中的应用 .....                   | 87         |

| 4.3.1 用于栅极扫描线的无畸变传输线.....                 | 87         |

| 4.3.2 无畸变传输线用作栅极扫描线对信号完整性的改善.....         | 89         |

| 4.4 LC 线：利用互电容/互电感的无畸变传输结构.....           | 90         |

---

|                                      |     |

|--------------------------------------|-----|

| 4.4.1 互电容/互电感无畸变传输原理.....            | 90  |

| 4.4.2 利用互电容/互电感实现无畸变传输的 LC 线结构 ..... | 92  |

| 4.4.3 LC 线对信号完整性的改善.....             | 94  |

| <br>第五章 无畸变传输线解析模型研究.....            | 98  |

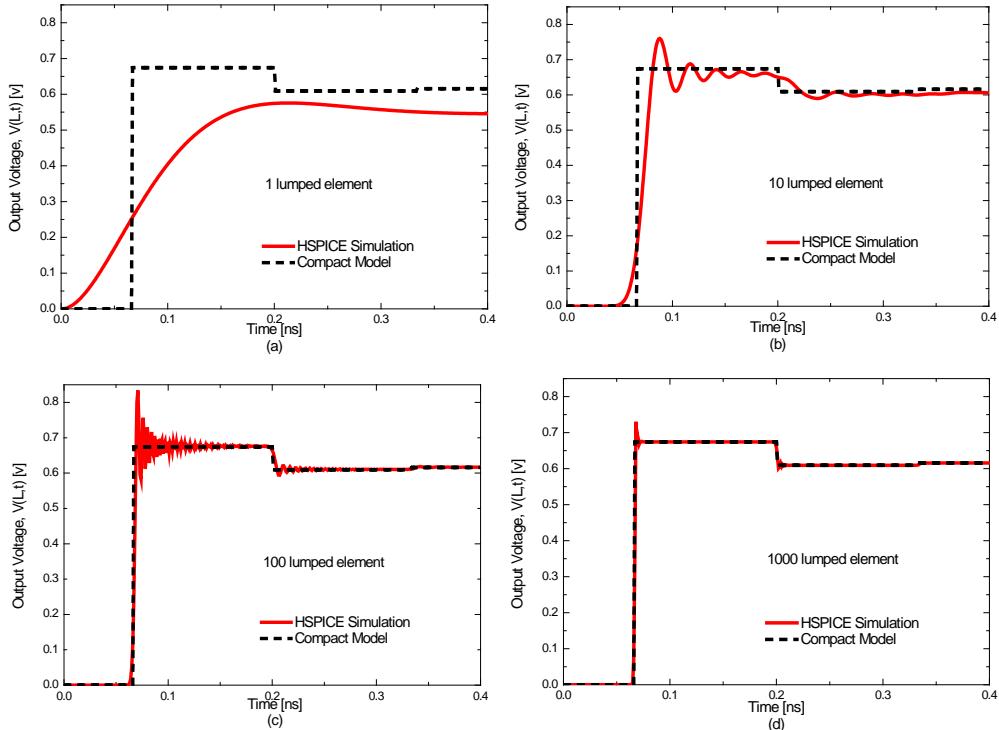

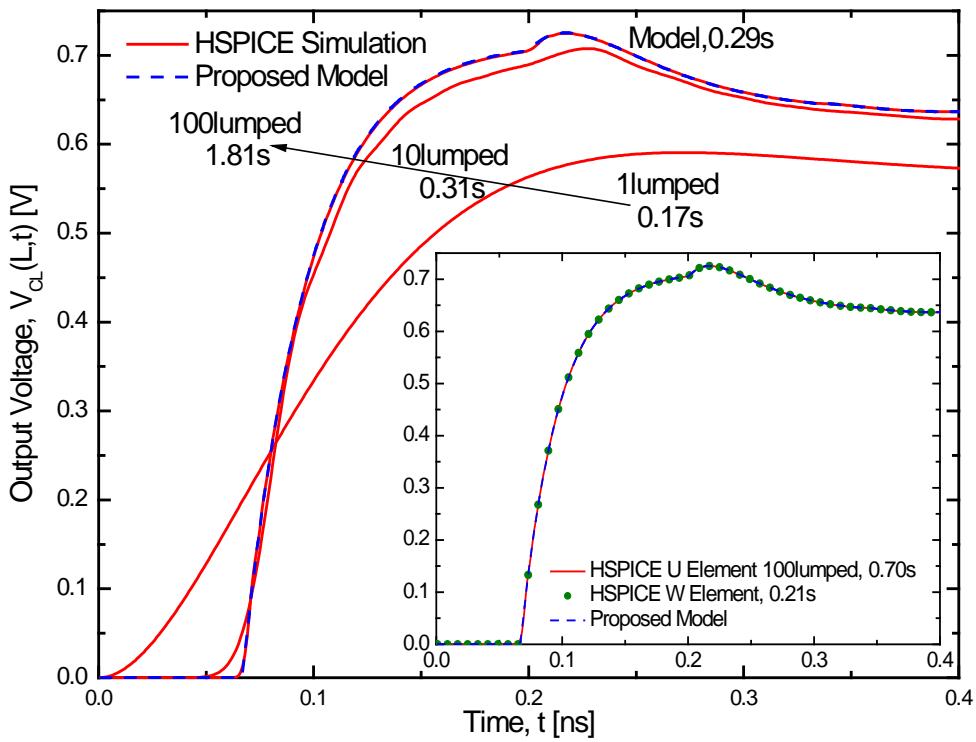

| 5.1 传输线解析模型研究简述 .....                | 98  |

| 5.2 理想负载的无畸变传输线解析模型 .....            | 104 |

| 5.2.1 半无限长无畸变传输线解析模型.....            | 104 |

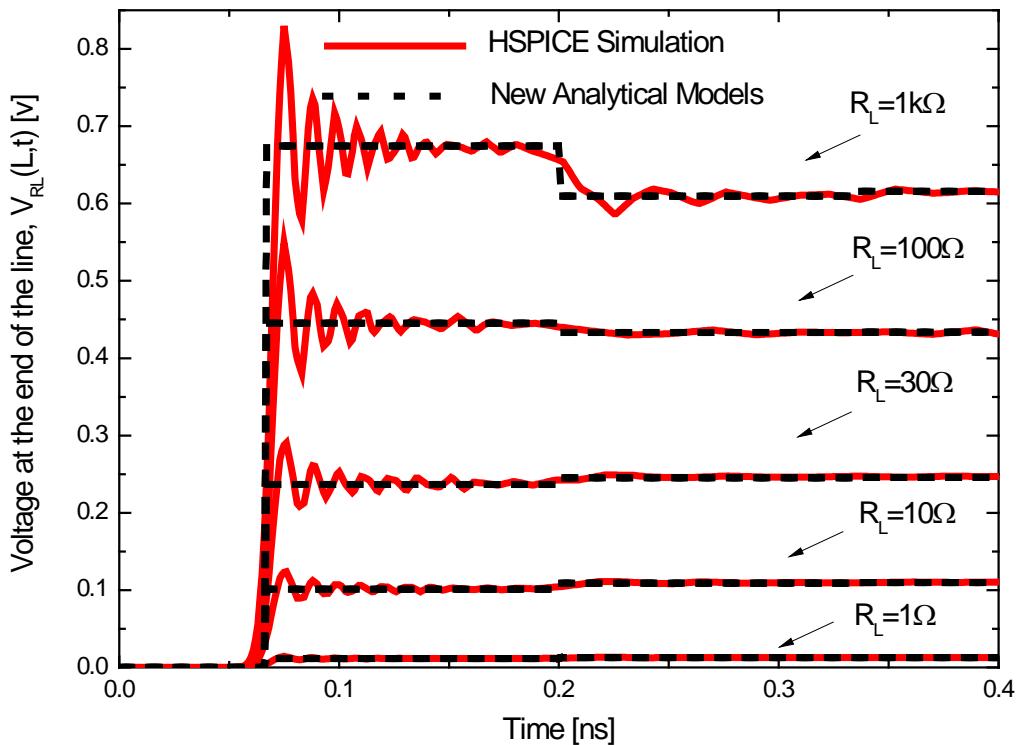

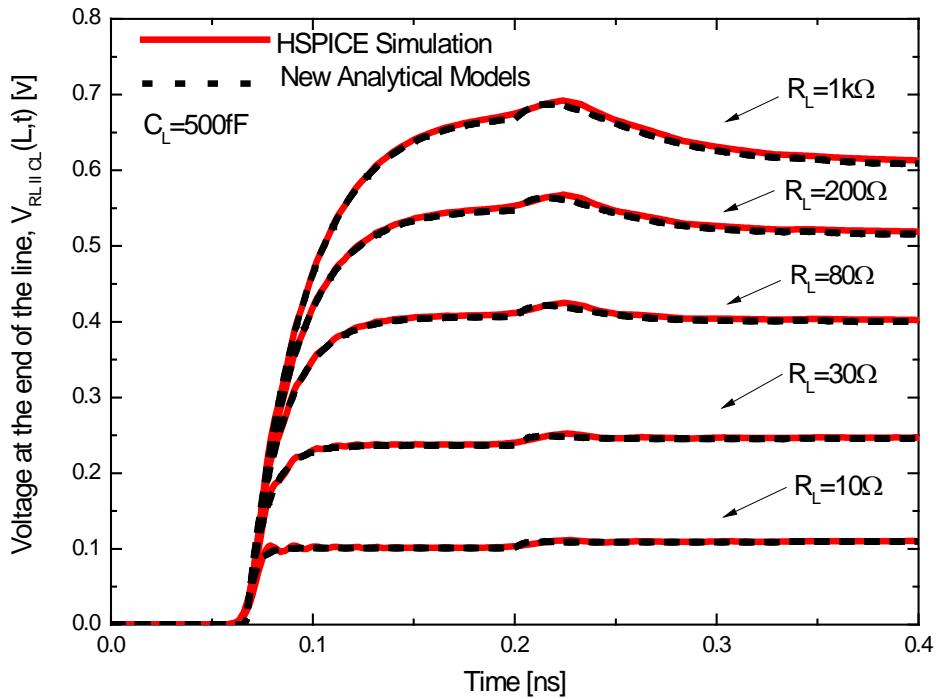

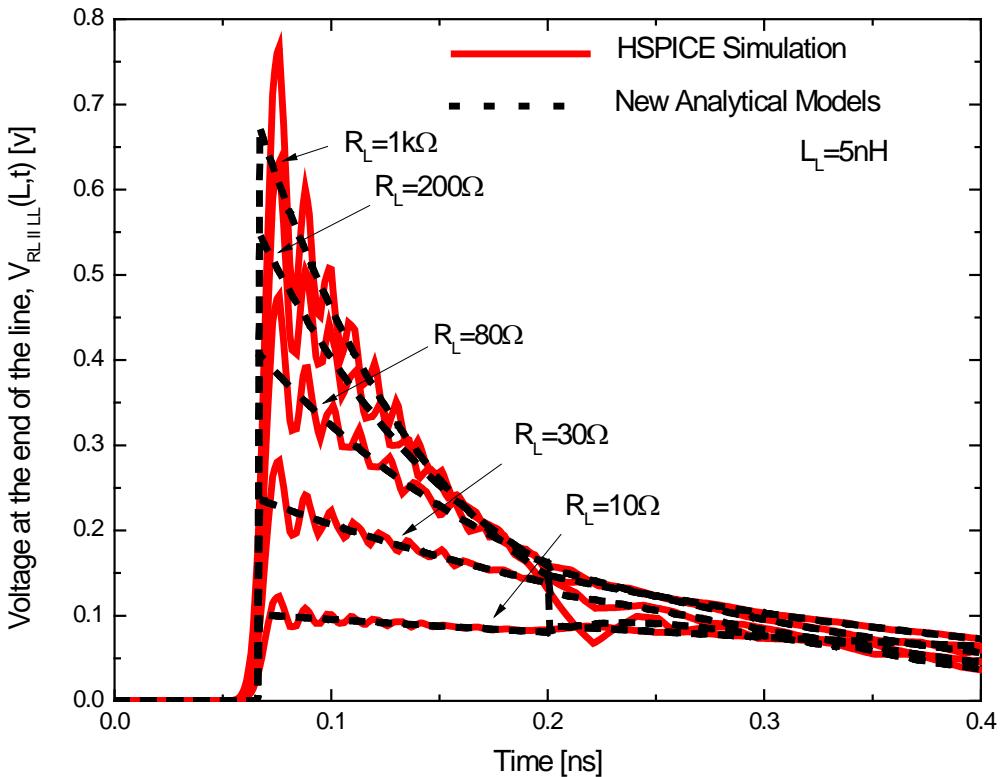

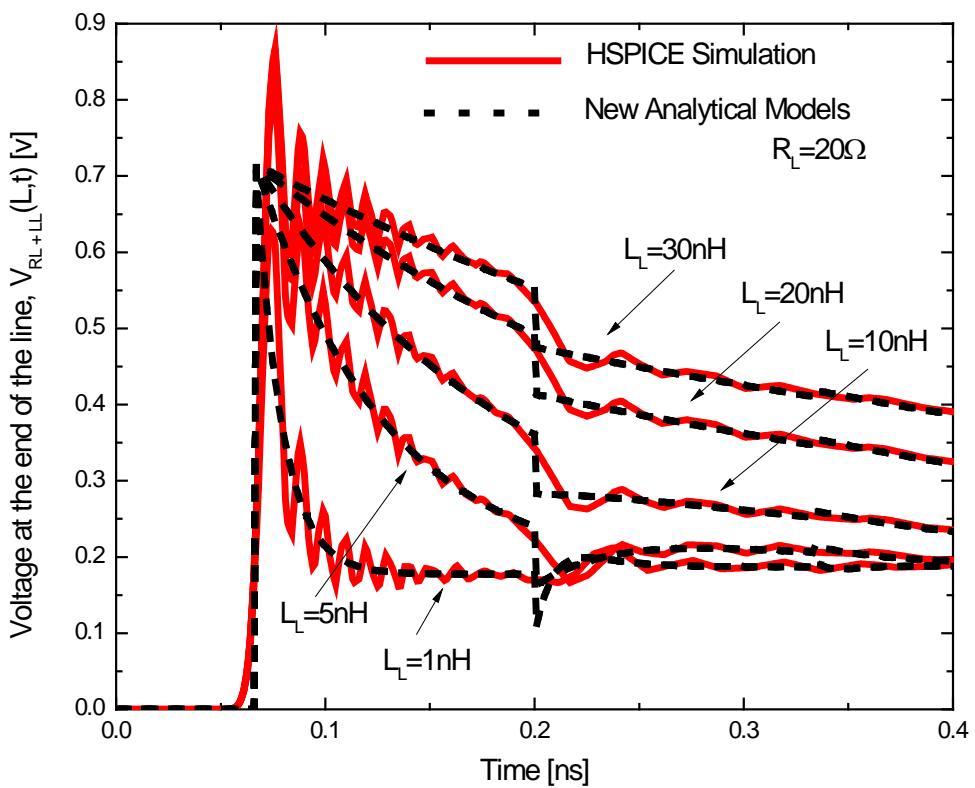

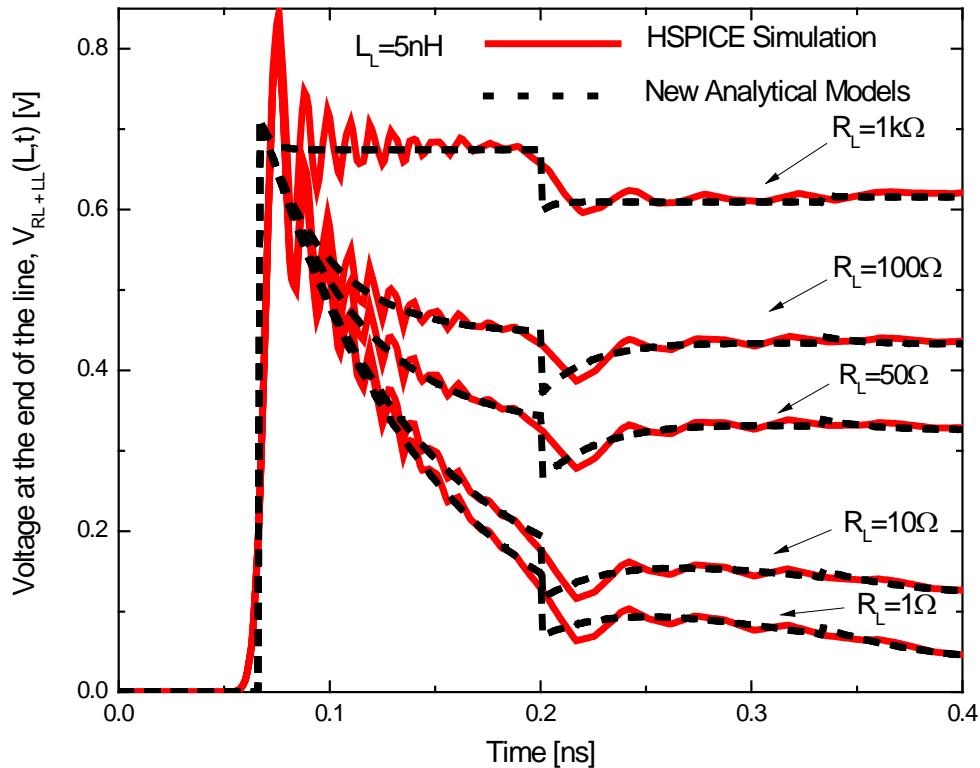

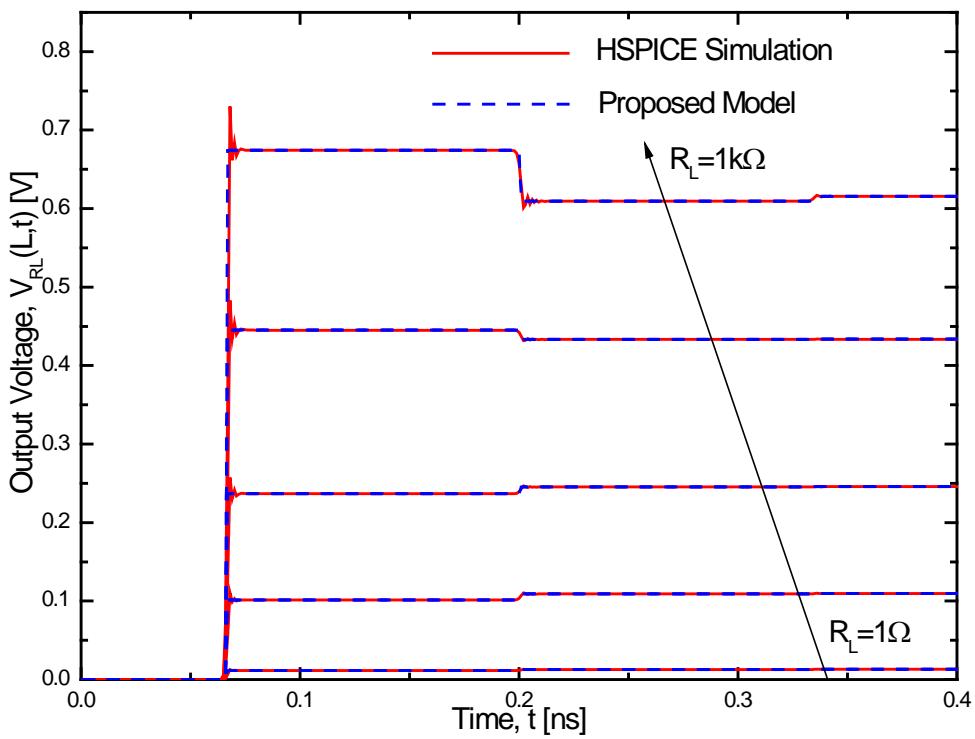

| 5.2.2 电阻负载的无畸变传输线解析模型.....           | 105 |

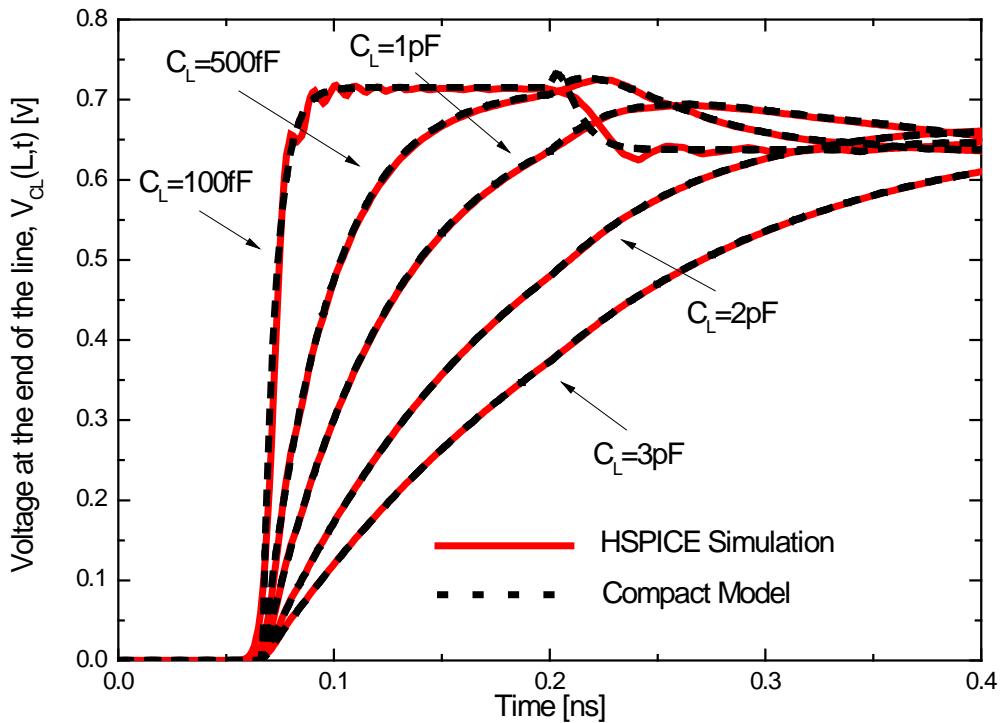

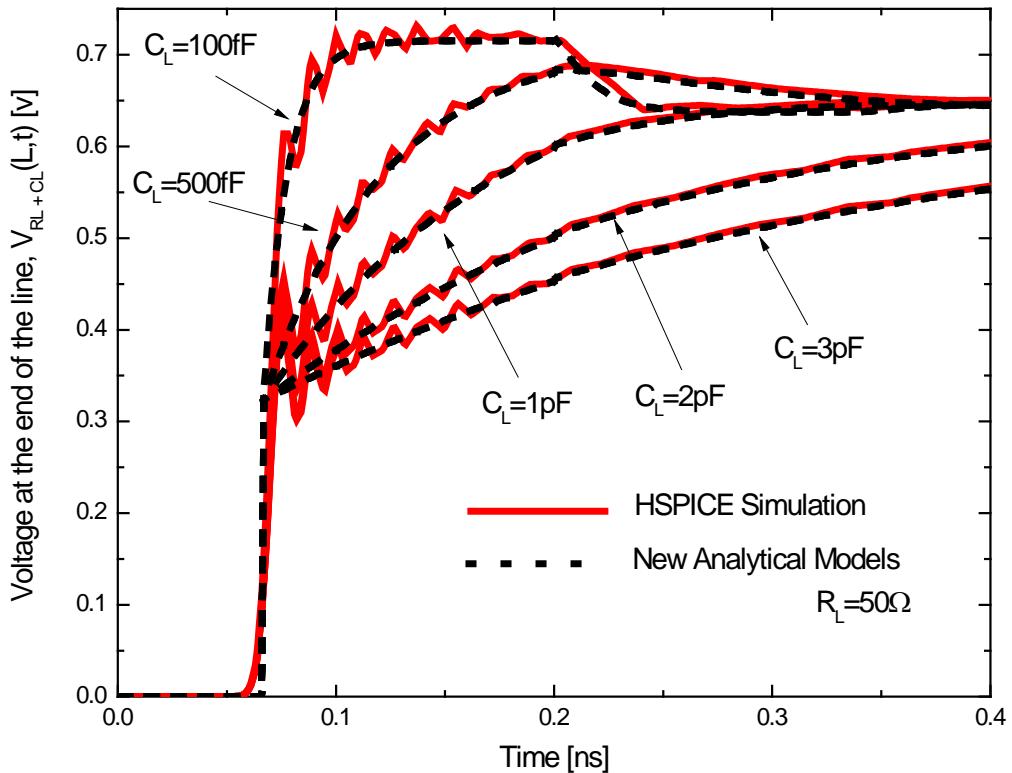

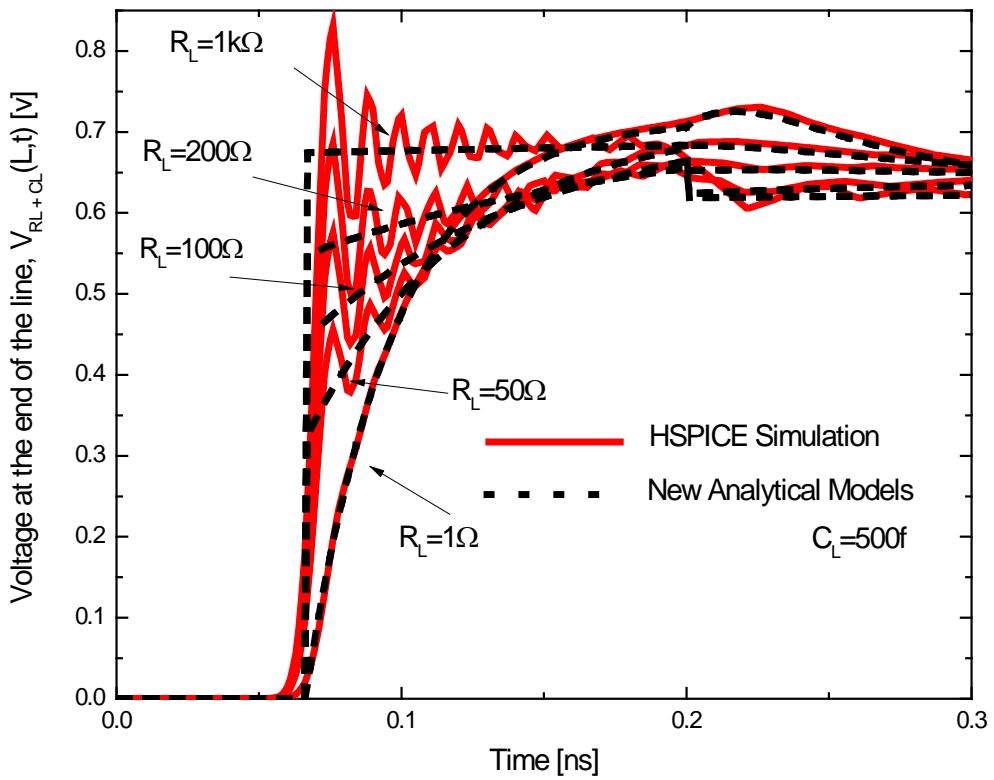

| 5.2.3 电容负载的无畸变传输线解析模型.....           | 107 |

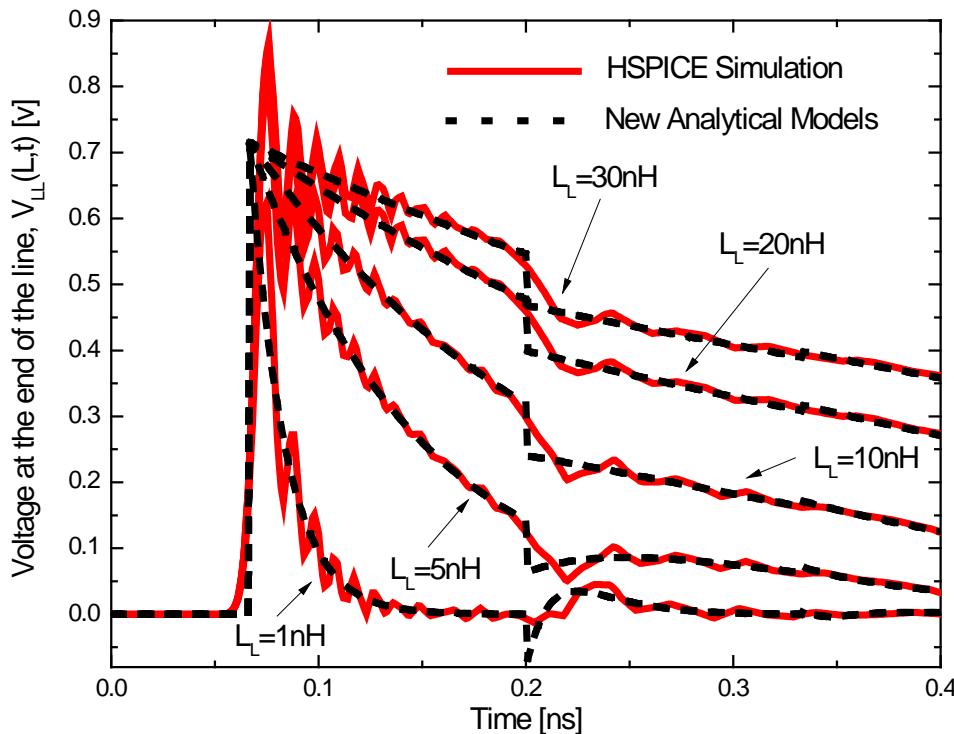

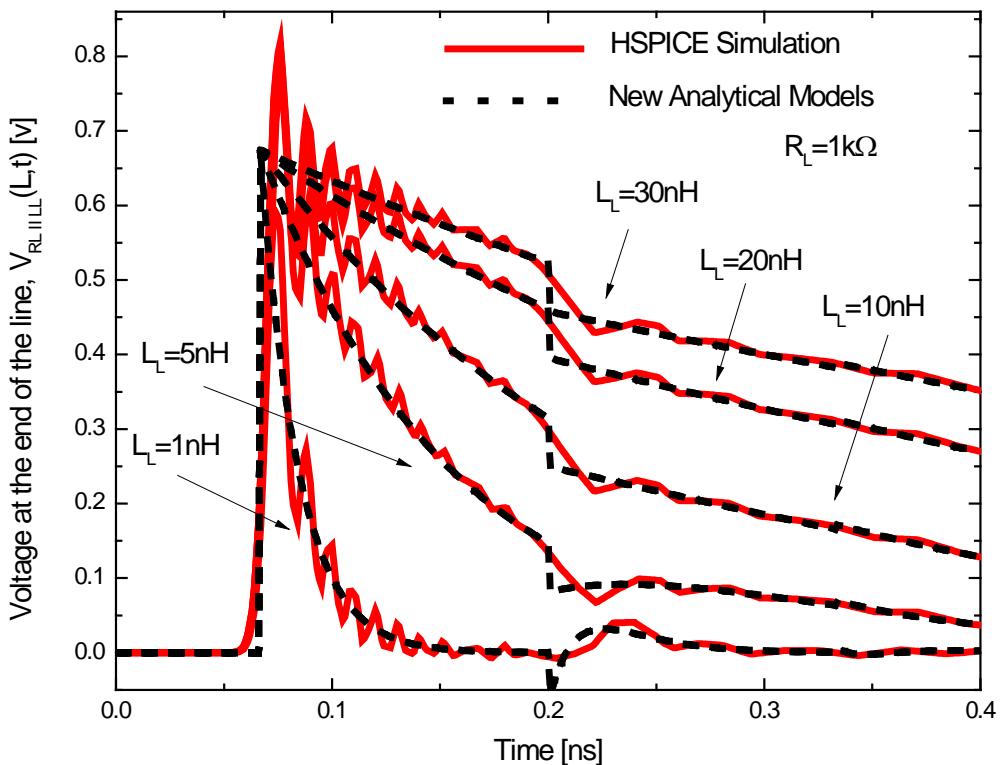

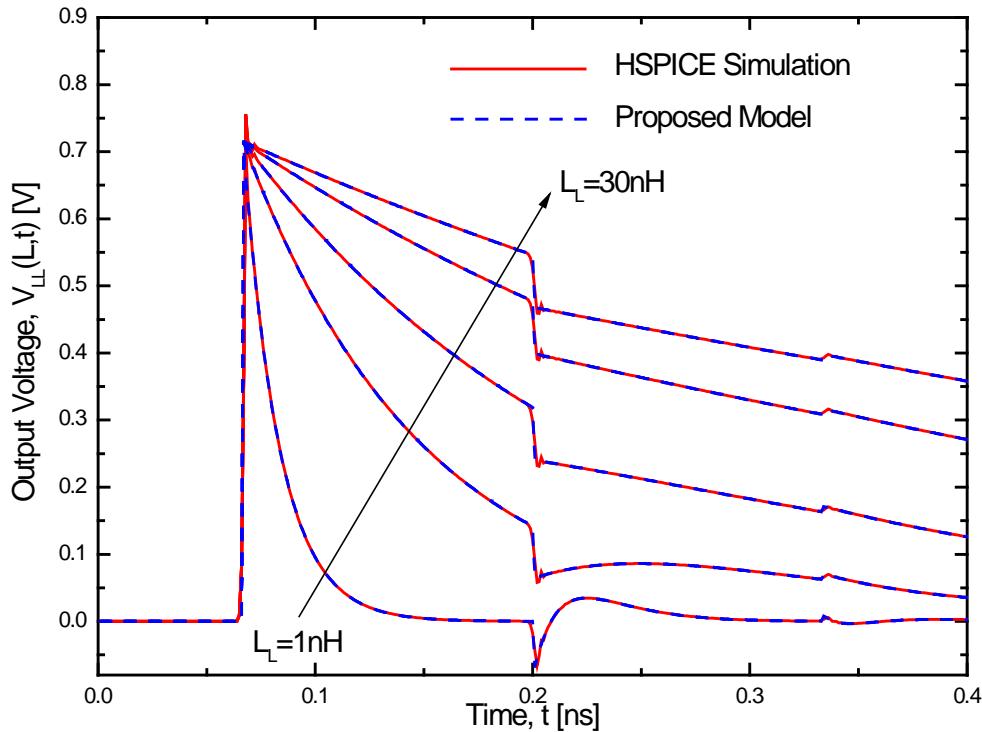

| 5.2.4 电感负载的无畸变传输线解析模型.....           | 110 |

| 5.3 非理想负载的无畸变传输线解析模型 .....           | 112 |

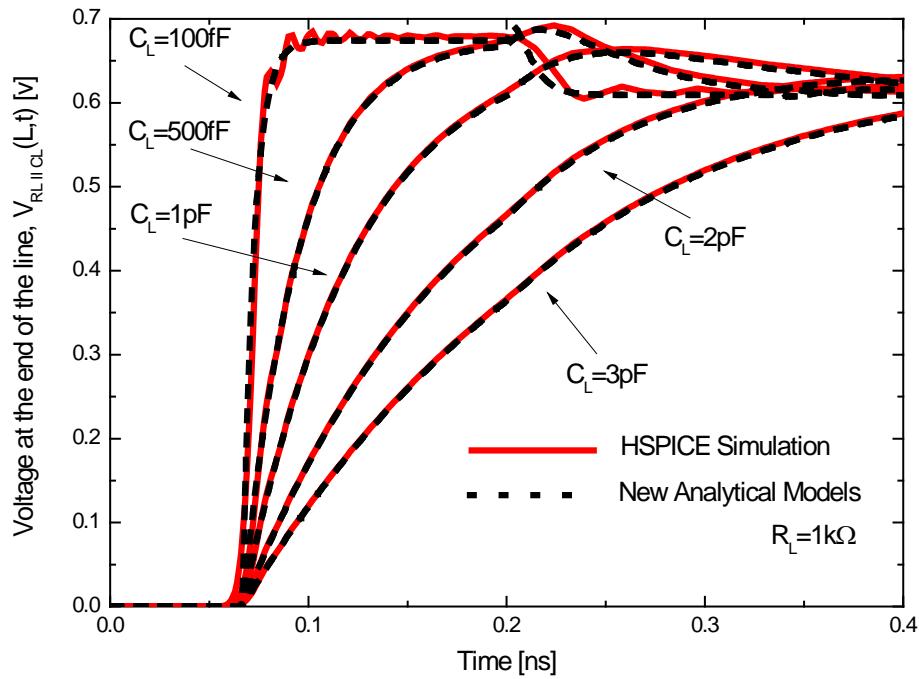

| 5.3.1 非理想电容负载的无畸变传输线解析模型.....        | 112 |

| 5.3.2 非理想电感负载的无畸变传输线解析模型.....        | 116 |

| 5.3.3 关于 HSPICE 仿真的一些讨论 .....        | 119 |

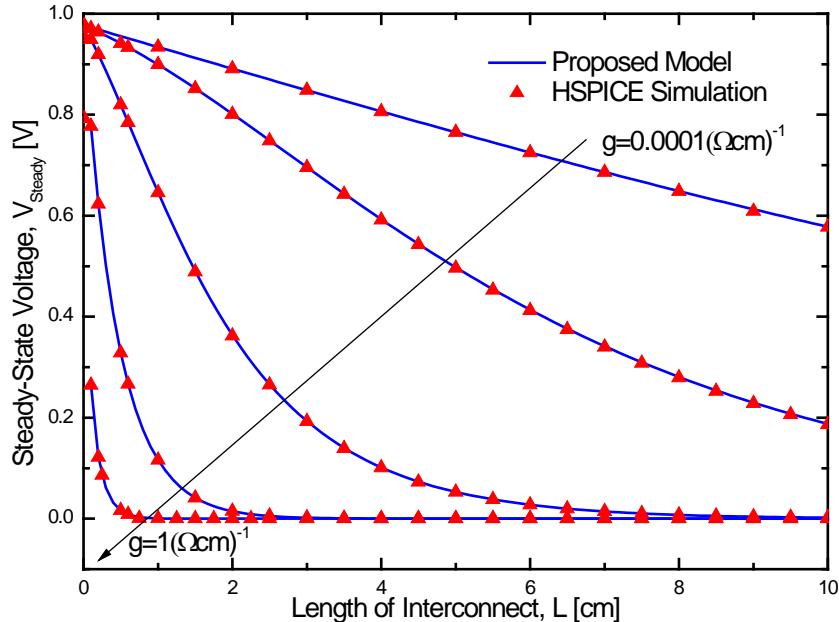

| 5.4 无畸变传输线信号完整性分析 .....              | 122 |

| 5.4.1 无畸变传输线的稳态电压.....               | 122 |

| 5.4.2 无畸变传输线的延迟、建立时间和阻抗匹配.....       | 123 |

| <br>第六章 结论.....                      | 128 |

| <br>攻读博士学位期间的科研成果.....               | 133 |

| 参考文献.....                            | 134 |

| 致谢 .....                             | 142 |

| 学位论文原创性声明和授权使用说明.....                | 143 |

# 第一章 绪论

以液晶显示(Liquid Crystal Display, LCD)为代表的平板显示(Flat Panel Display, FPD)产业正在全速发展中, 薄膜晶体管(Thin Film Transistor, TFT)作为FPD的核心器件正在受到越来越多的关注。当前, 氢化非晶硅(Hydrogenated Amorphous Silicon, a-Si:H) TFT为面板技术的主流, 然而, 由于其迁移率较低及具有阈值电压漂移等特性, 使得它难以用于高分辨率LCD, 亦难以用于有机发光二极管显示(Organic Light-Emitting Diode Display, OLED)等新一代显示。另一方面, 多晶硅(Polycrystalline Silicon, Poly-Si) TFT则以其高迁移率、大驱动电流等特性被人们寄予厚望, 被认为是实现像素开关矩阵和周边驱动电路集成的高性能LCD和OLED的核心技术之一。尽管Poly-Si TFT已经得到广泛研究, 但无论是其理论基础, 还是电路设计都存在许多关键问题需要解决, 本章将对Poly-Si TFT相关问题进行简述, 并概述本论文的研究问题、贡献以及章节安排。

## 1.1 多晶硅薄膜晶体管简述

### 平板显示技术与薄膜晶体管

信息化时代的到来与信息显示技术的不断发展密不可分, 如果没有信息显示技术做人机交互界面, 就无法形成现在的信息社会。在显示技术领域, 以LCD为代表的平板显示以其低功耗、宜集成、轻巧便携等优点已经取代传统的笨重的阴极射线管显示(Cathode Ray Tube, CRT), 涵盖了从小型音视频播放器、手机到平板电脑、家用/商用电脑、再到大尺寸电视在内的各种显示应用领域<sup>[1]-[5]</sup>。目前, LCD产品在FPD市场上独占鳌头, 并且仍在全速发展中, 据估计在今后几年内其总产值将超过集成电路产业<sup>[2]</sup>。与此同时, OLED则以其视角宽、成本低、厚度薄、响应速度快、对比度高、可实现软屏显示等优点, 在多元化的平板显示器市场中被视为极具发展前途的新型显示产品<sup>[6]-[9]</sup>。无论是LCD显示还是OLED显示技术, TFT都是其中的核心器件, 这正如硅芯片被称为电子计算机技术的核心器件一样, 没有TFT技术不断的突破和发展就没有今天FPD产业的兴旺与繁荣。

## 薄膜晶体管的起源

早在 20 世纪 30 年代<sup>[4]</sup>， Heil 在 1935 年申请的专利中即宣称他是 TFT 的发明人，他所涉及的材料包括氧化亚铜、五氧化二钒、碘以及后来被成功运用的碲，然而 Heil 的专利还只是概念性的。今天大家所熟知的 TFT 的发展实际上始于 20 世纪 60 年代<sup>[4]</sup>。1962 年， P.K.Weimer 应用多晶态 CdS 薄膜做有源层，用 SiO 薄膜做绝缘层， TFT 结构采用交叠型结构，即源漏接触电极与栅极分别在绝缘层两侧。之后， F.V.Shallcross 报道了由 CdSe 做有源层的相似器件。1964 年， Weimer 报道了由 Te 做有源层的 P 沟道 TFT 。这个阶段人们研发 TFT 的动力在于相比于晶体硅， TFT 能提供性能稍低但价格更低廉的解决方案，然而随着绝缘栅场效应晶体管和大规模集成电路的出现，人们开始相信，如果要制造低成本、高性能的晶体管及其电路，就必须采用晶体硅技术，这使得 TFT 的研发陷入低谷。

到了 20 世纪 70 年代<sup>[4]</sup>，人们认识到晶体硅技术的低成本与微型化密不可分，然而一些应用场合却需要低成本而大面积化的电子器件。这时，人们已经发明了液晶显示技术，但其中存在大量的串扰，使得显示质量不尽如人意。1971 年， Lechner 发表了一篇开启了 TFT 黄金应用的重要文章，他提出可以将 TFT 作为像素的开关应用在液晶显示技术中。1973 年， Brody 等人演示了第一个 TFT 矩阵寻址液晶显示器样机，其中的每个像素由一个 CdSe TFT 来控制。随着这些进展的到来， TFT 器件在显示中的应用激发了人们的研究热情，尤其是 TFT 稳定性、开关比和泄漏电流等方面。

1979 年 LeComber 、 Spear 和 Ghaith 描述了用 a-Si:H 做有源层材料的 TFT 特性， a-Si:H 能通过掺杂形成 n 或 p 型半导体材料，他们制备的 TFT 开态电流达几微安，关态电流大约为 1nA 。这种材料后来被证明具有深远意义，以至于现在的主流产品仍然以使用 a-Si:H 为主。然而，由于 a-Si:H TFT 迁移率较低及具有阈值电压漂移等特性，它不能满足栅驱动电路和源驱动电路对 TFT 器件响应时间的要求，无法实现周边驱动电路的集成，难以用于高集成度制造，亦难以用在以 OLED 为代表的新一代显示技术之中。

## 多晶硅薄膜晶体管研究现状

到了 20 世纪 80 年代<sup>[4]</sup>， IBM 的 Depp 等人在 1980 年报道了多晶硅薄膜晶

体管，他们采用化学气相沉积方法得到了具有高迁移率和优良性能的器件，然而由于采用了高温工艺，这种方法并不适用于廉价的玻璃衬底。1982 年，IBM 研究小组采用激光再晶化方法制备出迁移率高达  $400\text{cm}^2/\text{Vs}$  的 Poly-si TFT，高迁移率 TFT 既能实现 TFT 驱动像素的要求，又能集成周围驱动电路。在 20 世纪 90 年代<sup>[4]</sup>，高温（High Temperature, HT）Poly-Si TFT 已经能满足集成周边驱动电路的要求。1990 年，Stupp 等人报道的器件关态电流为  $0.1\text{pA}$ ，开关比为  $10^{10}$ ，迁移率为  $35\text{cm}^2/\text{Vs}$ 。HT Poly-Si TFT 的应用价值已经得到了人们的肯定，然而由于高温工艺，石英衬底和高成本限制了其在大面积液晶显示中的应用。1991 年，Little 报道了低温（Low Temperature, LT）Poly-Si TFT，关态电流为  $0.1\text{pA}$ ，开关比为  $3 \times 10^8$ ，迁移率为  $20\text{cm}^2/\text{Vs}$ ，大部分玻璃能够承受此种工艺温度，因而这种技术可以应用在大面积液晶显示中，尤其是需要集成周边驱动电路的显示和需要大驱动电流的 OLED 显示。

今天，多晶硅的制备工艺仍然有高温工艺和低温工艺之分<sup>[5]</sup>。其中，在高温工艺中，随着温度的升高，多晶硅薄膜晶粒尺寸会变大，迁移率会增高，但是高温工艺只能以昂贵的石英等耐高温材料为衬底，这使得其制造成本增加，不利于广泛的应用。低温工艺一般要相对复杂，可以在廉价衬底上制备，主要方法包括激光退火和金属诱导等方法。激光退火法是指在等离子体增强化学气相沉积（PECVD）法制备的 a-Si 材料的基础上，进行准分子激光退火，从而形成 Poly-Si 材料，此法制备的材料迁移率较高，制备温度通常低于 450 度，普通玻璃即可承受，尽管如此，其工艺机制尚未完全清楚，还不能良好的控制 Poly-Si 的均匀性和晶粒尺寸等性质。金属诱导法是指在 PECVD 法制备的 a-Si 材料的表面生长一层极薄的金属，或以离子注入的方式植入 a-Si 内部，在高温退火环境下，由金属诱导作用晶化 a-Si，其工艺温度可在 500 度以下，晶化时间短。

Poly-Si TFT 可以用做像素开关，也可以用于周围驱动电路。对于像素驱动用 TFT 开关器件，其开关比必须较高，对于 Poly-Si 材料，由于其迁移率较高，完全能满足显示电路对开态电流的要求，但对于常规自对准结构，其关态电流偏大，液晶像素上的电荷难以维持，影响了 LCD 的显示品质。为降低关态电流，人们设计出多种结构<sup>[5]</sup>：多栅极结构可以减小单个 TFT 器件漏端形成不完整 PN 结接触所产生的漏电流，考虑到其所占用的面积等因素，目前多采用双栅 Poly-Si TFT 结构；offset 型结构使得源漏与栅极之间出现偏移，偏移区域的高阻抗可以降低关

态电流，但同时也会影响开态电流；LDD 结构类似于 offset 结构，但采用轻掺杂减小了对开态电流的影响，目前被广泛使用。对于周边驱动电路用 TFT 器件，较快的响应速度是必须的，但对漏电流的要求并不严格，其多采用 LDD 结构，同时为减小面积，TFT 尺寸应尽量减小。

与 a-Si:H TFT 不同，Poly-Si TFT 具有更高的迁移率和开态电流，做成的液晶显示开口率更高，分辨率更高，响应速度更快，并且 Poly-Si TFT 能够满足驱动电路对器件响应时间的要求，与 CMOS 技术兼容，能够把周边驱动电路集成在显示面板上，这减少了外部驱动器芯片数和电路之间的连接，使得更便宜更稳定的显示器成为可能<sup>[4]</sup>。不仅如此，Poly-Si TFT 技术甚至有可能将整机系统与显示终端集成一体化，即不仅实现周边驱动电路的集成，还可以进一步将 CPU、音频电路等全功能系统集成在玻璃板上，形成面板系统（System on Panel, SOP）。此外，在新型的 OLED 技术中，因为 OLED 是电流驱动器件，TFT 需要一定的驱动能力，a-Si:H TFT 技术因为开口率小，稳定性差等原因并不是很好的选择，而高迁移率的 LT Poly-Si TFT 技术则以其开口率大和更好的稳定性更适用于 OLED 技术。

## 1.2 本论文研究的问题

目前，被认为是下一代 TFT 技术的 Poly-Si TFT 技术正在持续的发展，其理论、工艺和电路研究等方面都还有许多亟待解决的问题<sup>[10]-[21]</sup>。Poly-Si TFT 器件最基本的两个特征是器件的浮体结构和材料的晶界结构，它们会带来 KINK 效应和离散晶界效应等效应，严重影响着器件性能。同时，随着显示尺寸和分辨率的提高，由栅信号线和数据线延迟导致的图像显示失真等问题越来越严重，严重制约了 Poly-Si TFT 面板向大尺寸、高分辨率方向的发展。本论文将主要对 Poly-Si TFT 的 KINK 效应和离散晶界效应进行研究，同时研究面板中的信号完整性问题，以下进行简述。

### 多晶硅薄膜晶体管的 KINK 效应

由于 Poly-Si TFT 具有浮体结构，与传统体硅结构器件不同，由漏端碰撞电离所产生的空穴会堆积在体区，从而打开寄生晶体管的发射结，导致电子大量从源端注入，由此带来输出电流的突增，输出特性曲线出现翘曲现象，此即 KINK 效

应。**KINK** 效应会引起数字电路中功耗增大和开关特性退化，以及模拟电路中最大电压增益和噪声容限下降。

关于 **KINK** 效应的机制，国际上已有很多研究小组进行了分析，**Valdinoci** 等人通过二维数值仿真指出，**Poly-Si TFT** 之中的缺陷将强烈影响 **KINK** 效应<sup>[22]-[24]</sup>，在复合中心浓度很大时，由于大部分碰撞电离所产生的空穴将无法到达源端，从而不会出现一般的电流突增现象，尽管如此，他们没有进一步说明当有明显的 **KINK** 效应发生时复合机制的强弱，没有更深入的揭示出寄生晶体管的工作机理；**Zheng** 等人利用传统双极晶体管的理论对 **KINK** 效应建立了精简模型<sup>[25]-[32]</sup>，但是模型无法解释仿真中发现的当漏端电压增大时寄生晶体管电流增益下降的现象，这意味着 **KINK** 效应中寄生晶体管的电流传导机制与传统晶体管不同，需要进一步研究。

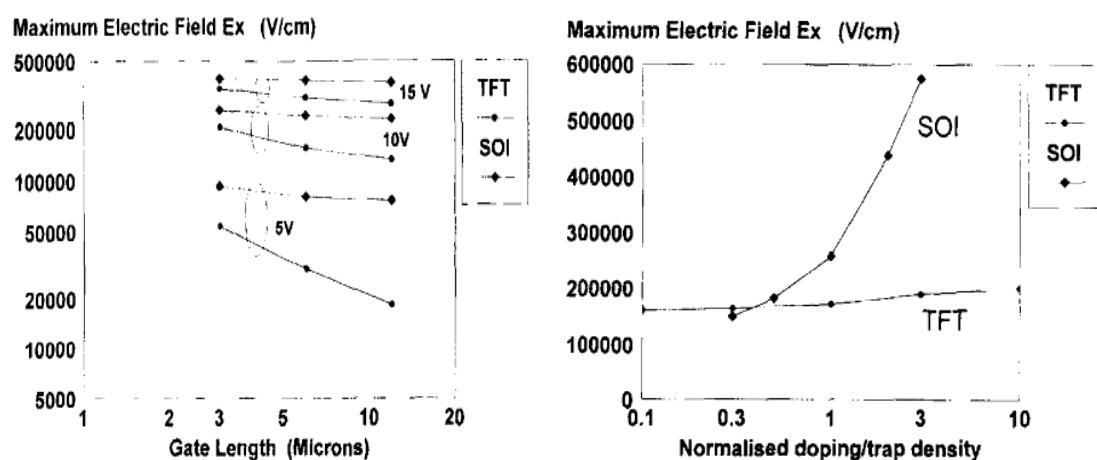

关于沟道长度对 **KINK** 效应的影响方面，**Valletta** 等人通过数值仿真方法指出沟道长度对 **KINK** 效应的影响是通过对寄生晶体管增益的影响来进行的，但是他们没有对此给出进一步的解释<sup>[33]-[35]</sup>；**Armstrong** 和 **Hack** 等人对比了 **TFT** 器件和 **SOI** 器件 **KINK** 效应的异同，但他们的分析没用充分考虑寄生晶体管的影响<sup>[36]-[37]</sup>。

由上可知，通过实验和数值仿真方法<sup>[38]-[39]</sup>，人们对 **KINK** 效应展开了广泛的研究，但是其机制仍没有完全清楚，基于传统的双极晶体管扩散/复合机制难以解释出现在寄生晶体管中的特殊现象。同时，沟长对 **KINK** 效应的影响机制也没有完全清楚，需要进一步考虑寄生晶体管和陷阱的影响。论文第二章将对这些问题作进一步的阐述并给出分析和结论。

## 多晶硅薄膜晶体管的离散晶界效应

**Poly-Si** 还具有独特的晶界结构，其晶界处具有远多于单晶硅的缺陷，这使得 **Poly-Si TFT** 具有独特的离散晶界效应。为增强器件性能，现代 **Poly-Si TFT** 器件往往具有大晶粒结构<sup>[40]-[43]</sup>，这更使得离散晶界效应显著增强<sup>[44]-[51]</sup>。

在晶界基本性质对器件影响方面，**Kimura** 等人通过实验和数值仿真研究了晶界的位置对器件性能的影响<sup>[52][53]</sup>，他们指出，当晶界位置靠向漏端时，晶界处的势垒高度会被降低，从而增大传导电流；**Yamaguchi** 通过数值仿真研究了晶界上的缺陷、晶界的数目和晶界的位置对器件性能的影响，并提出了减少这种影响的器件结构<sup>[54]</sup>；**Zhou** 等人通过数值仿真研究了晶界的角度对器件性能的影响，

他们发现垂直于沟道的晶界对电流的衰减影响最大，平行于沟道的晶界对其影响最小<sup>[55]</sup>。尽管如此，这些研究并没有把离散晶界效应和浮体结构结合起来考虑。

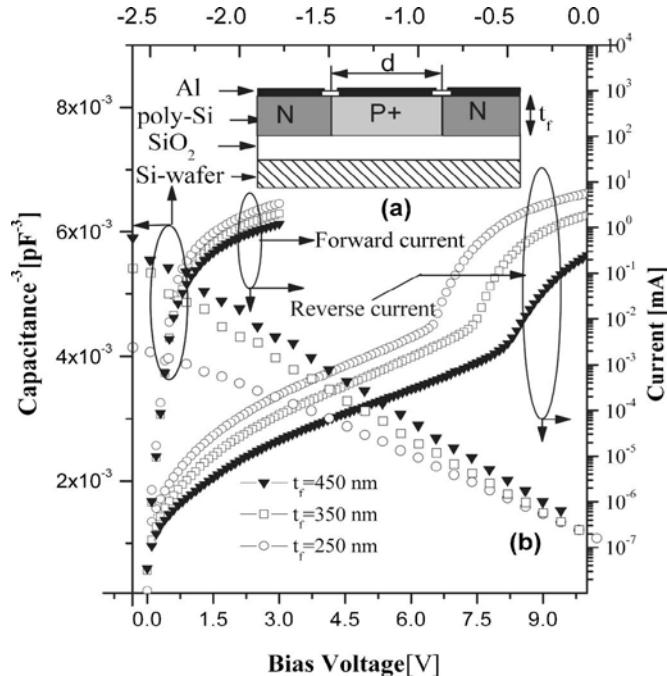

在 Poly-Si TFT 晶界处的碰撞电离现象研究方面，之前曾有报道其他多晶材料如 GaAs, ZnO 晶界处的碰撞电离现象<sup>[56][57]</sup>；此外，Das 等人把 Poly-Si 电阻的电流突增现象解释为和晶界处的碰撞电离有关，并用一个因子代表这种效应，建立了电阻的电流模型<sup>[58]</sup>；Amrani 等人通过研究 Poly-Si PN 结的击穿现象得出结论，正是晶界处的碰撞电离现象使得 Poly-Si PN 结的击穿电压要低于硅 PN 结<sup>[59]</sup>。尽管如此，Poly-Si TFT 的晶界处碰撞电离效应研究还是空白。

离散晶界效应对器件性能的影响可以通过晶界处的势垒高度来进行分析，势垒高度模型是研究离散晶界效应的关键<sup>[60]-[65]</sup>，在此基础上，考虑离散晶界的电流模型可以被开发出来<sup>[66]-[75]</sup>，对于现代大晶粒器件，所得模型可以获得比将陷阱有效均匀近似更好的结果<sup>[76]-[83]</sup>。在这一方面，Lin 等人通过求解准二维泊松方程，得到了可以考虑 DIGBL 效应的势垒高度模型，并以此为基础，建立了电流模型<sup>[60]</sup>；Chen 等人通过电中性原理，得到了本征 Poly-Si TFT 器件中的势垒高度模型，并建立了电流模型<sup>[61][62]</sup>；Wu 等通过电荷守恒原理考虑了发生 DIGBL 现象时，晶界两侧势垒高度变化的不等性，并建立了解析模型<sup>[63]</sup>。然而，这些模型均没有考虑晶界位置的影响，而 Ho 利用电位叠加原理和镜像电荷方法得到的模型虽然考虑了晶界位置的影响，但是较复杂<sup>[64]</sup>。

由上可知，考虑浮体结构的离散晶界效应，即晶界上陷阱浓度、晶界数目和晶界位置对 KINK 效应的影响还需要进一步研究。同时，Poly-Si TFT 的晶界处的碰撞电离机制还有待进一步研究。此外，简洁高效的、能考虑 DIGBL 效应和晶界位置影响的势垒高度模型是十分必要的。本论文第三章将对此进行详细阐述，并给出相关结论。

## 用于面板的无畸变传输线

互连线给现代电路带来了信号完整性问题<sup>[84]-[92]</sup>，随着工艺的不断进步，这一问题越来越严重。对于面板来说，线上信号延迟严重制约着显示技术向大面积、高分辨率方向的发展<sup>[93][94]</sup>。

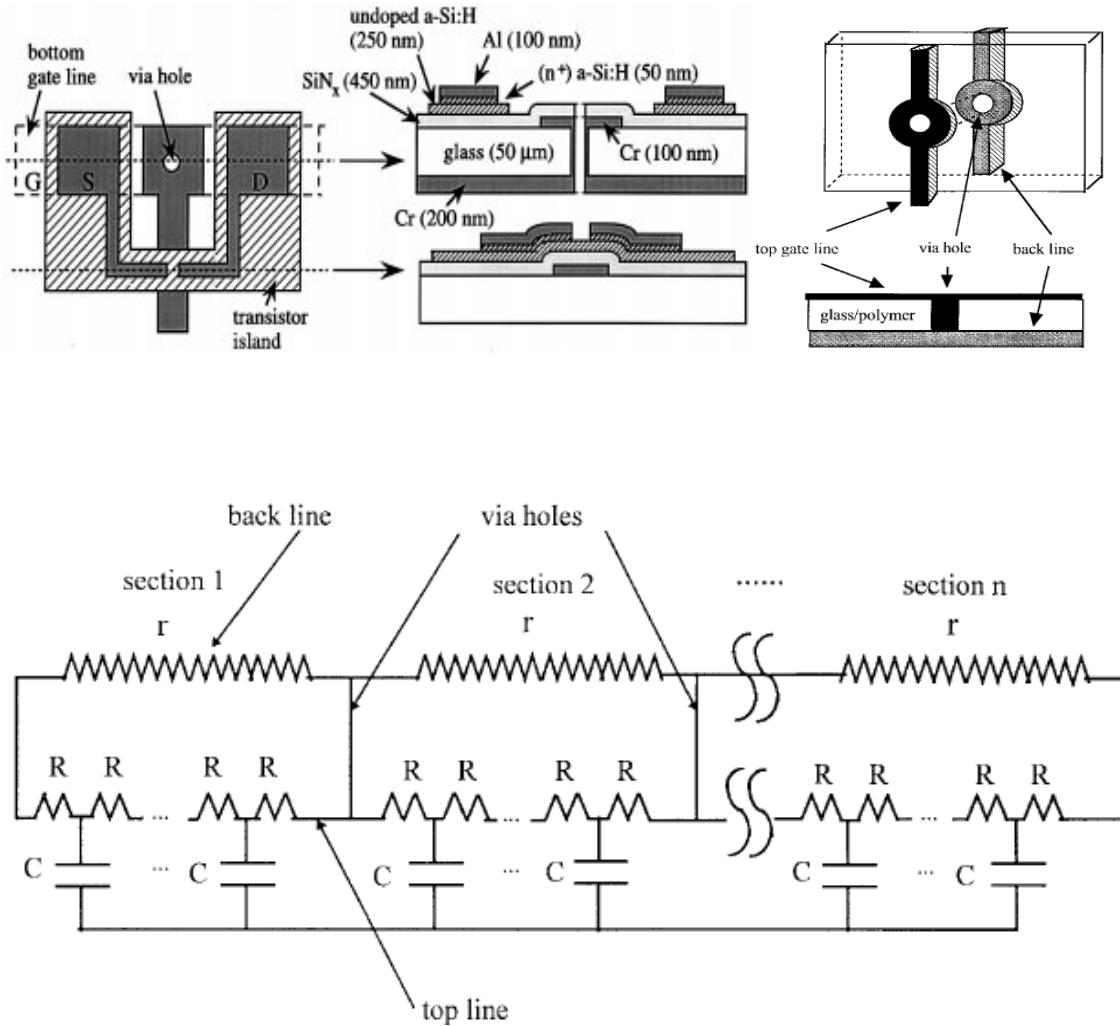

在面板中，为减少线上延迟，很多研究小组做出了努力。Zhang 等人提出在衬底上打孔的方法来减少栅线延迟<sup>[95][96]</sup>；Park 等人通过在栅线和数据线间引入

空气间隙来减少交叉电容的方法来减少数据线延迟<sup>[97][98]</sup>；Chen 等通过对数据线驱动电路的优化设计来减少数据线延迟<sup>[99]</sup>。

为减少线上延迟，还可以使用无畸变传输线。无畸变传输线是使用传输线来作为互连线技术的一种<sup>[100]-[103]</sup>，然而，对于一般的传输线，因为在其上传输的不同频率的信号的速度和振幅衰减不同，一个包含多频率分量的波形在传输过程中便会有畸变。为消除畸变，很多研究小组做出了努力<sup>[104]-[110]</sup>，其中，Cheng 等人提出，可以通过在线上插入电导来满足 Heaviside 条件<sup>[111]</sup>的方法来实现信号的无畸变传输<sup>[112]-[115]</sup>。Cheng 等提出的无畸变传输线技术被应用于片上级互连线及封装级互连线中，可以显著减少信号的延迟，增强信号的完整性，但具体在面板中如何应用无畸变传输线还有待研究。

为设计无畸变传输线，需要使用解析模型。关于传输线的解析模型，Sakurai 通过求解电报方程得到了考虑线上分布电阻和电容的模型<sup>[116]</sup>，并由此计算了信号延迟和串扰；Davis 等通过考虑线上分布电感，将这一模型大大扩展了<sup>[117][118]</sup>，此后，Venkatesan 等又将模型扩展至考虑电容负载的情况<sup>[119][120]</sup>。无畸变传输线的模型需要考虑线上分布电导，还有待研究。

论文第四章将详细阐述面板中的信号延迟问题和无畸变传输线理论，同时提出在面板中应用无畸变传输线来增强信号完整性的原理和方法。论文第五章将详细阐述传输线解析模型的建立方法，对无畸变传输线建立解析模型，并利用模型进行无畸变传输线的分析与设计。

### 1.3 本论文的贡献和章节安排

本论文在上述三个专题上的研究取得了多项成果或进展，在多晶硅薄膜晶体管的 KINK 效应研究方面取得了以下成果：

(1) 提出了 KINK 效应的新机制。采用 Sentaurus Device TCAD 工具，本论文对多晶硅薄膜晶体管器件做了二维数值仿真，并采用分离晶界方法处理了其中的陷阱，由此提升了仿真的精度，扩大了仿真结果的应用范围。利用仿真结果，本论文首次指出与 KINK 效应相关的寄生双极晶体管中的主要电流传导机制不是扩散-复合机制而是漂移机制。以此为基础，本论文解释了寄生双极晶体管共发射极电流增益随漏电压增加而下降这一不同于传统双极晶体管的现象，提出这是由

碰撞电离强度的增加导致的。由此可知寄生晶体管机制和碰撞电离机制是相互关联的，KINK 效应的机制是相互关联的非传统寄生双极晶体管机制和碰撞电离机制的联合机制。这些结论阐明了 KINK 效应相关机制，解释了相关现象，对进一步建立数学模型提供了基础，并且指出在实际器件的分析与设计中，涉及 KINK 效应时，必须考虑寄生双极晶体管的非传统机制和大漏端电压时的强碰撞电离作用以及两者相互的影响。

(2) 提出了沟长对 KINK 效应的影响机制。通过考虑寄生晶体管，本论文解释了沟长对 KINK 效应的影响现象，即沟长越短，KINK 效应越大，而当电压变大时，沟长的影响趋于消失。

(3) 指出了陷阱对 KINK 效应的影响。通过对 TFT 和绝缘体上硅的仿真结果的对比分析，本论文还提出并解释了缺陷的存在将使得 TFT 器件的 KINK 效应更容易受沟道长度影响，由此提出，对于短沟道 TFT 器件，必须充分考虑其更加严重的 KINK 效应。

在多晶硅薄膜晶体管的离散晶界效应研究方面取得了以下成果：

(4) 揭示了晶界对 KINK 效应的影响。利用仿真工具，本论文分析了晶界上陷阱浓度、晶界数目和晶界位置对晶界处势垒高度的影响，提出并解释了晶界上陷阱浓度越少、晶界数目越少、晶界位置越靠近漏端，器件 KINK 效应越大，同时分析了它们对寄生晶体管效应和碰撞电离效应的影响，由此指出，对于大晶粒、少晶界、少陷阱的现代多晶硅薄膜晶体管器件，更要注意 KINK 效应所带来的影响，同时，器件的不均匀性将会影响其性能，必须控制。

(5) 提出并解释了与晶界处碰撞电离有关的现象。这是指 Poly-Si TFT 输出特性曲线中的大电流现象，以及在转移特性曲线中的翘曲现象，同时还包括由晶界处的碰撞电离效应所引起的特殊的 KINK 效应。本论文提出的晶界处碰撞电离效应指出了晶界对器件性能的独特影响，同时具有潜在应用价值。

(6) 得到了考虑 DIGBL 效应和晶界位置影响的晶界处势垒高度模型。采用求解准二维泊松方程并利用高斯定理的方法，本论文得到了考虑晶界位置和 DIGBL 效应的 Poly-Si TFT 表面势模型和势垒高度模型。通过 TCAD 仿真验证，模型对不同的晶界位置和电压大小均具有很好的精度。模型推导过程简单，结果简洁，可用来指导分析与 DIGBL 现象和晶界位置有关的现象，并为进一步得到考虑晶界位置影响的 Poly-Si TFT 传导电流模型提供了基础。

在用于面板的无畸变传输线研究方面取得了以下成果：

**(7) 提出了用于面板的无畸变传输线。**为改善面板信号的延迟和失真、增强信号的完整性，本论文对栅极扫描线上电感进行调优并插入电导来满足 Heaviside 条件，从而将栅极扫描线改造成无畸变传输线，其输出波形对输入波形的形状还原性显著提高，信号延迟和原输出波形相比显著减少，信号完整性得到显著提高，同时可具有易被应用的稳定电压值。

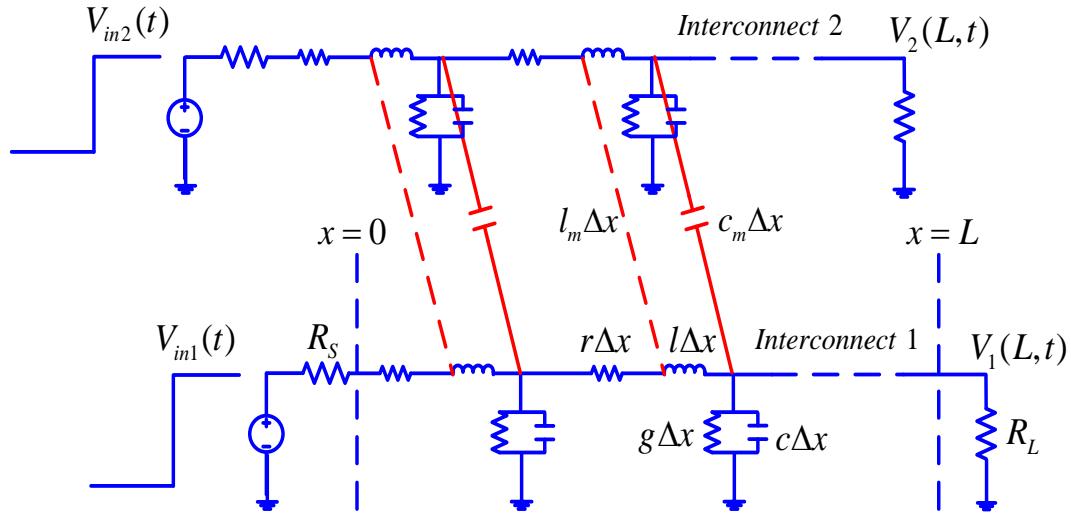

**(8) 提出了无畸变传输结构-LC 线。**LC 线利用了传输线之间的互电容和互电感将两条传输线组合起来，实现了信号的无畸变传输，这种原理可以应用在片上级、封装级或板级等任何传输线能够应用的情况，同样也可以应用在面板中来减少信号的延迟并增强信号的完整性。

**(9) 建立了无畸变传输线解析模型。**通过先建立半无限长无畸变传输线解析模型，再利用阻抗反射和拉普拉斯变换的方法，本论文得到了负载为理想电阻、电容与电感时和非理想电容与电感时的无畸变传输线解析模型，模型物理意义明显，与高精度 HSPICE 仿真曲线符合的非常好，同时更具有快速、解析的优势。利用这些模型，可以得到稳态电压、延迟、建立时间的解析表达式，利用这些结论可以进行无畸变传输线的调优设计，即考虑稳态电压、畸变程度、建立时间等因素对线上参数进行优化，从而得到满足要求的传输线性能。

本论文的各章安排如下：第二章研究多晶硅薄膜晶体管的 KINK 效应，第三章研究多晶硅薄膜晶体管的离散晶界效应，第四章提出用于面板的无畸变传输线，第五章提出无畸变传输线精简模型，第六章给出结论。

## 第二章 多晶硅薄膜晶体管 KINK 效应研究

Poly-Si TFT 器件的浮体结构是其最明显的特征之一，由于器件体区为悬浮状态，在高电场情况下由漏端碰撞电离产生的电荷无法迅速移走，堆积在体区的电荷会打开体源 PN 结而使得电子从源端大量注入，并在漏端再次发生碰撞电离，从而导致漏端电流的突然增大，在输出特性曲线中将出现曲线突然翘曲的现象，此即 KINK 效应。KINK 效应将会导致电路功耗增大、开关特性退化、最大电压增益以及噪声容限下降<sup>[22]-[37]</sup>，并得到了广泛的研究<sup>[22]-[37]</sup>。然而 KINK 效应机制的现有理论仍无法解释实验和仿真中的全部现象，如 Poly-Si TFT 器件寄生晶体管的电流增益随漏电压的增加而下降，当漏电压较大时沟长对 KINK 效应的影响趋于消失，TFT 器件的 KINK 效应比 SOI 器件更易受到沟长的影响等。利用二维数值仿真方法，本章将阐述 KINK 效应的新机制，解释实验和仿真中的现象，从而指导实际器件的分析与设计。

### 2.1 传统 KINK 效应机制的局限性

#### 基于传统双极晶体管理论的 KINK 效应机制的局限性

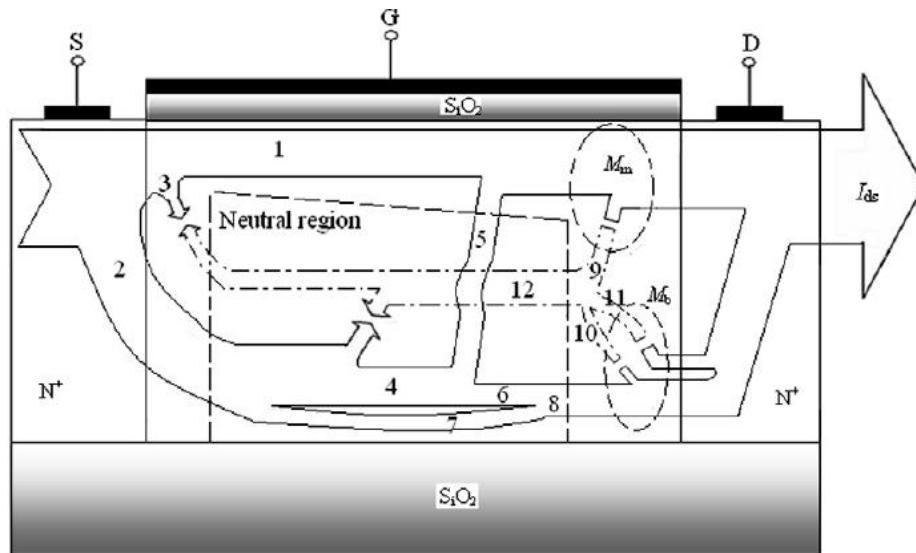

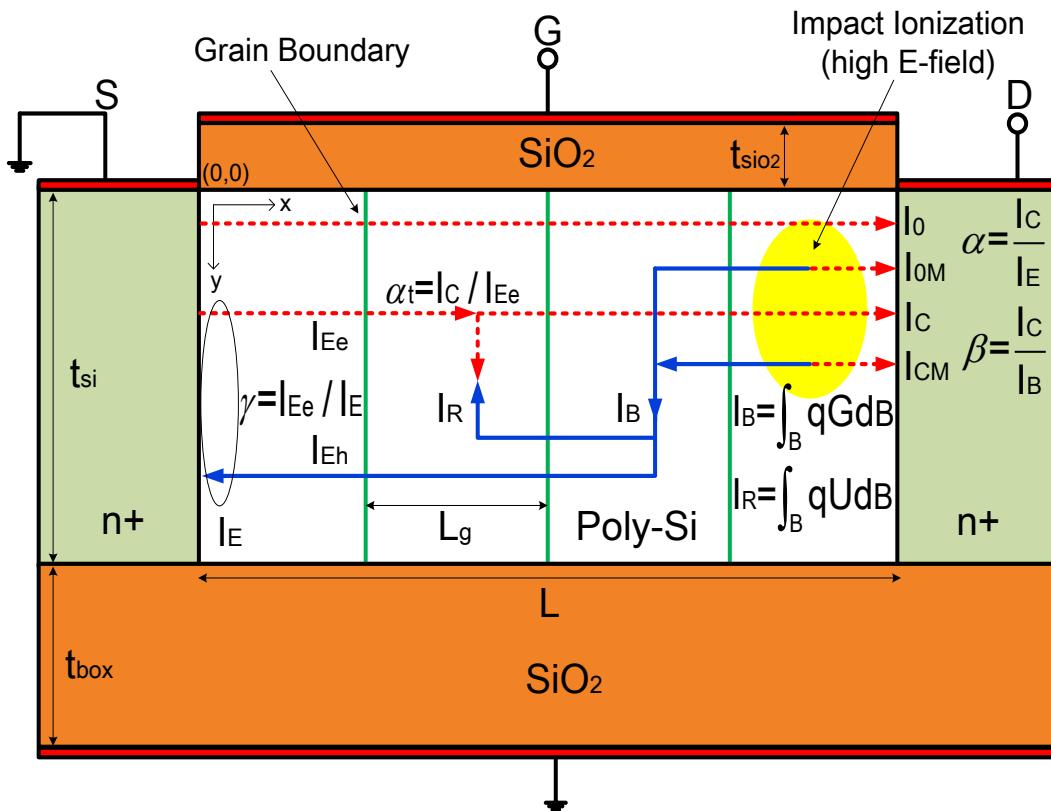

研究 KINK 效应的关键之一在于对其中寄生晶体管机制的分析，利用传统双极晶体管的扩散-复合电流传导机制，国际上很多研究小组都做出了贡献<sup>[22]-[25]</sup>。如图 2-1 所示，Zheng 等人基于传统双极晶体管的电流传导机制对 Poly-Si TFT 器件内部复杂的电流输运过程进行分析，细致阐述了器件内部的沟道电流传导机制、寄生晶体管电流输运机制以及碰撞电离机制<sup>[25]</sup>。

如图 2-1 所示，在 n 沟道 Poly-Si TFT 中，源端-中性体区-漏端将形成寄生的 NPN 双极晶体管，对于体硅器件，体一般接地，而 Poly-Si TFT 器件的体处于悬浮状态，寄生晶体管易被开启，KINK 效应主要起因于此。当 Poly-Si TFT 工作在饱和区时，其漏端由于高阻区的存在会使得大部分电压降降落于此，从而形成强电场，沟道电子电流  $1:I_{ch}$  在漏端高电场区通过碰撞电离产生电子和空穴，并生成空穴电流  $9:I_{b1}$ 。对于体硅结构，产生的空穴可以从体电极引出，然而由于 TFT 器件的浮体结构，使得碰撞电离所产生的空穴在栅电压的作用下堆积在体区，这提升了的体

-源 PN 结的电势差，当电势差达到一定值时，体-源 PN 结，即寄生双极晶体管的发射结将被开启，大量电子将从发射结注入，形成发射结电子扩散电流  $2:I_{edif}$  和发射结复合电流  $3:I_{erec}$ ，在经过基区复合后，体区输运电子电流为  $4:\alpha_T I_{edif}$ ， $\alpha_T$  为输运系数，此后，有一部分注入电流  $5:k_1 \alpha_T I_{edif}$  会被吸引到沟道表面，到达集电结的体区输运电子电流  $6:(1-k_1) \alpha_T I_{edif}$  与集电结扩散电流  $7:I_{cdif}$  汇合成集电结电子电流  $8:I_c$ ，并也发生碰撞电离，产生空穴电流  $10:I_{b2}$ ，其与  $9$  和集电结产生电流碰撞电离产生的空穴电流  $11:I_{b3}$  一起，构成基区空穴电流  $12:I_b$ ，并保持发射结的打开并与注入的电子电流复合。电子注入和碰撞电离会使得漏端电流有一个突增，输出特性曲线突然翘曲，如图 2-2 所示，即发生 KINK 效应。

图 2-1 考虑了寄生晶体管的 Poly-Si TFT 传导电流成分分析<sup>[25]</sup>

图 2-2 发生 KINK 效应时电流的不规则突增现象<sup>[25]</sup>

图 2-3 传统晶体管的增益随漏电压的增大而增大，随沟长的增大而减小<sup>[25]</sup>

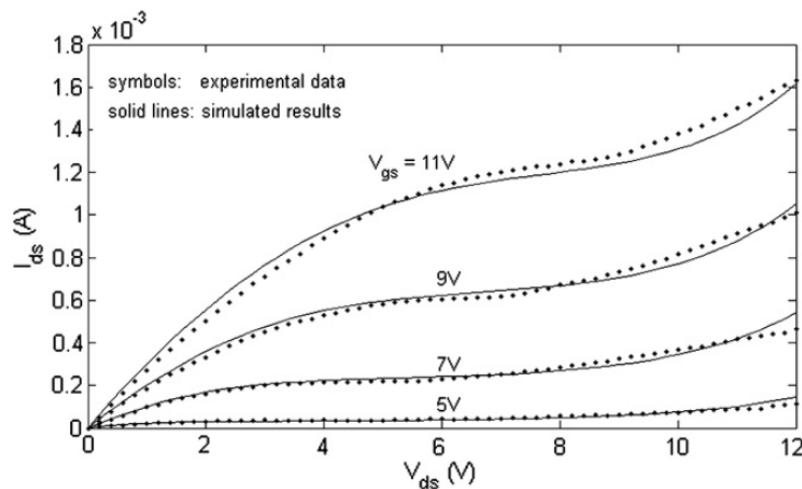

如上的解释基于传统的双极晶体管的工作原理，可以得到与实验基本一致的模型曲线，如图 2-2 所示，但同时也会得到如图 2-3 所示的结论，即寄生晶体管的增益随漏电压的增大而增大，随沟长的增大而减小。这是因为在传统的晶体管中，电流传导机制主要是扩散和复合，漏电压的增大会使得中性区减少，减少复合从而增大电流和增益，即 *early* 效应，而沟长的增大则会使得中性区增加，增大复合从而减小增益，增益随沟长的变化在沟长比较小时是很敏感的。而我们在下面将会看到，这些结论与数值仿真和量测结果并非一致，实际上，对寄生晶体管的实验和仿真表明，寄生晶体管的增益将随漏电压的增大而减小，同时，寄生晶体管在漏端电压较大时，其增益基本不随沟长变化。我们将在下一节中指出，产生这种区别的主要原因是寄生晶体管有着不同于传统晶体管的电流传导机制，不再以扩散-复合为主。可见，基于传统双极晶体管理论的 KINK 效应机制还不能完全与实验吻合，不够准确，还有待研究。

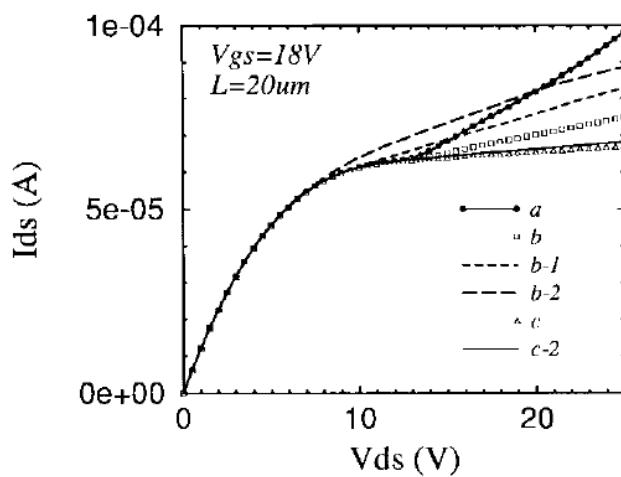

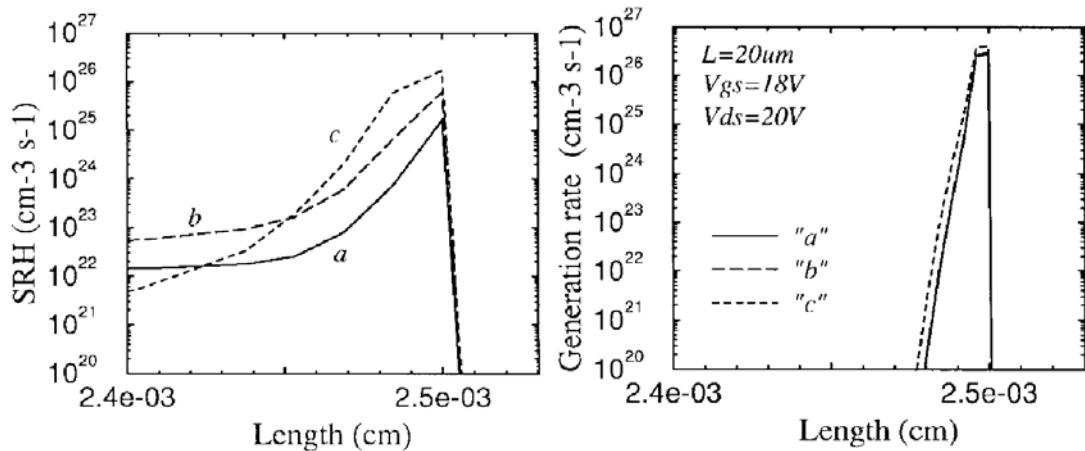

与此同时，对于传统晶体管中的复合机制对 KINK 效应的具体影响，在国际上一些研究小组通过数值分析的方法做了一定的工作。Valdinoci 等人在总结了前人的研究成果的基础上指出无论是在中性体区还是在漏端碰撞电离区，复合机制都强烈的影响着 Poly-Si TFT 器件的 KINK 效应<sup>[22]-[24]</sup>。Poly-Si TFT 器件存在晶界结构，其上分布着大量陷阱，影响着器件的性能。对于长沟道小晶粒的器件，一种近似的分析方法是假设陷阱均匀的分布在整个 Poly-Si 薄膜之中，这被称为有效中介近似法（Effective-Medium-Approximation, EMA）。Valdinoci 等人采用了 EMA 方法，并采用了四个指数分布的陷阱能级来描述均匀分布在 Poly-Si 薄膜中的陷阱，

其中两个为分布在能带上方的受主陷阱 (acceptor)，另两条为分布在能带下方的施主陷阱 (donor)，其电子 ( $n$ ) 和空穴 ( $p$ ) 俘获横截面分别为  $\sigma_{na}$ ,  $\sigma_{nd}$ ,  $\sigma_{pa}$ ,  $\sigma_{pd}$ 。如表 2-1 所示，当采用不同的俘获横截面积时，其仿真结果如图 2-4 所示，曲线 a,b,c 采用的俘获横截面积依次增大，则其电流突增依次减小，当俘获横截面积达到 c 所采用的程度时，电流突增消失。图中只有 a 曲线的仿真结果可以与实验拟合，若采用更大的俘获横截面积，即便增大碰撞电离率（如 b-1, b-2, c-2 所示），也不能得到和实验数据吻合的仿真结果。可见复合机制强烈的影响着 KINK 效应。Valdinoci 等人接着对复合机制对 KINK 效应的影响做了详细的分析。如图 2-5 所示，随着俘获横截面积的增大，复合率将显著地增加，然而产生率却几乎不变。产生率之所以在漏端附近有峰值，是因为当器件处于饱和状态时，漏电压将主要加在漏端的高阻区，产生大电场，造成显著的碰撞电离现象。复合率与电子和空穴的浓度成正比，其峰值也出现在碰撞电离最显著的漏端高场区。由此可见，俘获横截面积是通过显著的影响复合率来影响 KINK 效应的。

表 2-1 仿真中使用的不同的复活横截面积

| Capture cross-sections (cm <sup>2</sup> ) |                            |                            |

|-------------------------------------------|----------------------------|----------------------------|

|                                           | $\sigma_{na}, \sigma_{pd}$ | $\sigma_{nd}, \sigma_{pa}$ |

| Curves "a"                                | $10^{-17}$                 | $10^{-15}$                 |

| Curves "b"                                | $10^{-16}$                 | $10^{-14}$                 |

| Curves "c"                                | $10^{-15}$                 | $10^{-13}$                 |

图 2-4 采用不同俘获横截面积时的仿真结果<sup>[23]</sup>

图 2-5 复合率和产生率受俘获横截面积影响的情况<sup>[23]</sup>图 2-6 到达源端的空穴及源体 PN 结开启情况受俘获横截面积影响的情况<sup>[23]</sup>图 2-7 由源体 PN 结注入的电流和 KINK 效应受俘获横截面积影响的情况<sup>[23]</sup>

进一步, 如图 2-6 左所示, 当俘获横截面积过大, 如 c 的情况时, 由于复合率过大, 会使得漏端碰撞电离产生的空穴在到达源端之前就被复合掉。当复合率稍小些, 如 b 的情况时, 空穴将有一部分到达源端, 而只有当复合率小到 a 的情况时, 产生的空穴才会多数到达源端。如图 2-6 右所示, 只有当俘获横截面积小到 a 的情况, 复合率不太大的情况下, 源体 PN 结才会被显著的打开, 从而仿真结果可以与实验观测的数据保持一致。而若复合率太大, 如 b, c 的情况, 源体 PN 结未能完全开启, 甚至不能开启, 便无法得到可以与实验拟合的仿真结果。上面的结论可以从图 2-7 得到验证, 可以看到, 只有当俘获横截面积不太大, 复合率不太高, 如 a 的情况, 源端才会显著的注入电子电流, 才会得到与实验结果相符的, 有正确翘曲的仿真输出特性曲线。

尽管如此, Valdinoci 等人的结论只说明了当复合率很大, 足以影响到空穴积累的时候, KINK 效应不会出现或程度很弱, 却没有具体说明当发生明显的 KINK 效应时复合效应的作用, 在下一节中, 本论文将对寄生晶体管中的复合机制进行进一步分析, 并指出其与传统双极晶体管理论的区别。

Valdinoci 等人还对寄生晶体管的性质进行了分析。如图 2-8 所示, 寄生晶体管的增益随漏电压的增大而减小(左), 在碰撞电离产生相同载流子的情况下 KINK 效应随沟长的增加而减弱 (右)。正如前所述, 这种仿真现象与传统双极晶体管不同-传统双极晶体管的增益将随漏端电压的增加而增加。尽管如此, Valdinoci 等人仍然用传统晶体管中的扩散复合理论对这些现象进行了简单的解释, 本论文将在下一节中对此进行详细分析, 得到考虑非传统寄生晶体管性质的 KINK 效应机制。

图 2-8 寄生晶体管工作情况分析<sup>[23]</sup>

## 现有沟长对 KINK 效应影响机制的问题

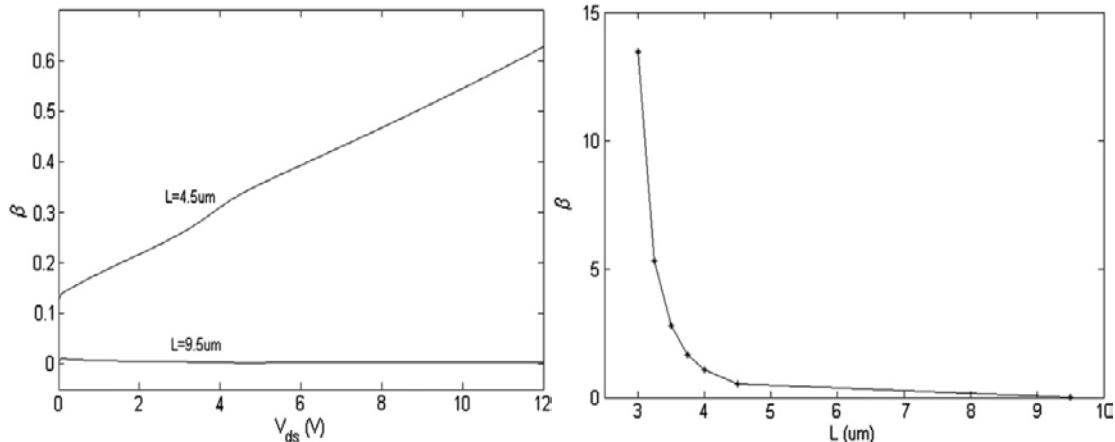

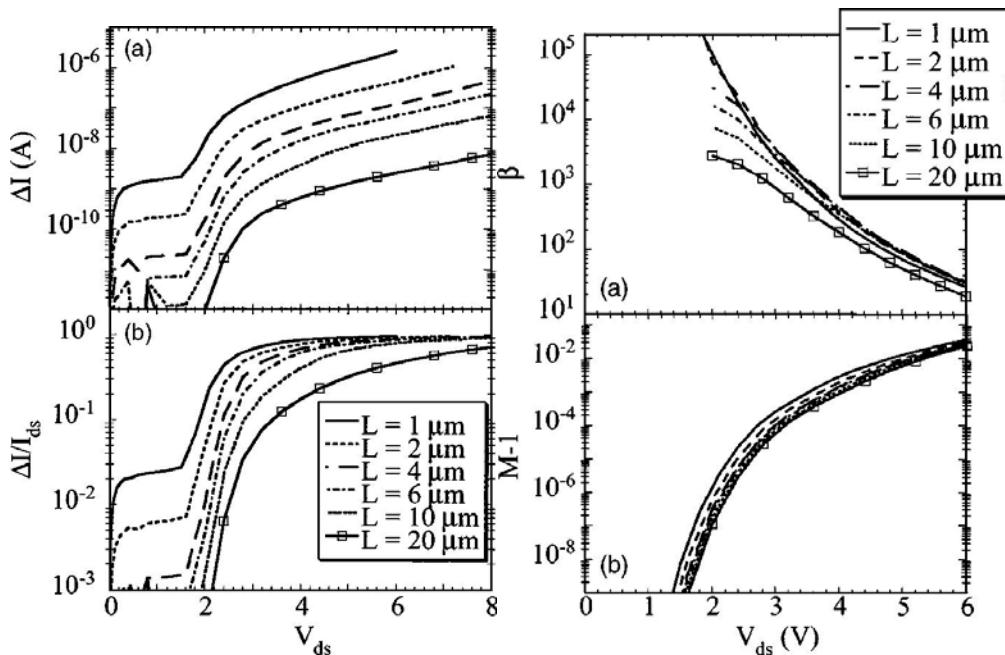

在解释 KINK 效应受 Poly-Si TFT 器件沟长影响方面, Valletta 等人在文<sup>[33]-[35]</sup>中指出, KINK 效应随沟长的变化关系可由寄生晶体管增益、碰撞电离空穴电流和碰撞电离系数随沟长的变化关系来解释。如图 2-9 左所示, 浮体产生的电流增量  $\Delta I$  会随沟长的减小而增大, 电流增量  $\Delta I$  与总电流  $I_{ds}$  的比值可以表达为寄生晶体管增益  $\beta$  和碰撞电离系数  $M$  的函数, 即  $\Delta I / I_{ds} = (\beta + 2)(M - 1) / M$ 。如图 2-9 右所示,  $M$  随沟长的变化并不明显, 故相对电流增量  $\Delta I / I_{ds}$  随沟长的变化主要是由寄生晶体管增益  $\beta$  随沟长的变化引起的, 当漏端电压较小时, 寄生晶体管增益  $\beta$  将随沟长的减小而增大, 故相对电流增量  $\Delta I / I_{ds}$  也将随沟长的减小而增大, 而当漏端电压较大时, 寄生晶体管增益  $\beta$  将基本不随沟长变化, 相对电流增量也基本不随沟长变化。此外, 借由 BJT 电流的关系以及在高漏电压下电流增益  $\beta$  对  $L$  变化不敏感的事实, 可以知道电流增量随沟长的变化关系主要取决于碰撞电离空穴电流随沟长的变化, 如图 2-10 所示,  $\Delta I \approx I_e$  随  $L$  的变化取决于  $I_b$  随沟长的变化。

图 2-9 沟长对 KINK 效应、寄生晶体管增益和碰撞电离系数的影响<sup>[33]</sup>

图 2-10 沟长对 KINK 效应所引起的电流的影响<sup>[33]</sup>

这些仿真和实验现象也与前面提到的传统晶体管的性质不同，而 Valletta 等人并未进一步解释形成这些现象的原因，没有说明为何漏电压的大小会影响增益随沟长变化的方式。本论文将在下一节中对此作进一步分析，解释寄生晶体管增益和 KINK 效应随沟长的变化方式与漏电压大小有关的现象。

此外，对于不同的晶界陷阱，沟道长度对 Poly-Si TFT KINK 效应的影响方式也不同，在对这一现象的解释方面，Hack 和 Armstrong 做出了富有意义的工作<sup>[36]-[37]</sup>。与 SOI 器件相比，Poly-Si TFT 器件最大的区别即是其具有晶界，其上分布有陷阱，Hack 和 Armstrong 同样采取了有效中介近似方法近似的认为陷阱均匀分布在 Poly-Si 薄膜中。这种近似虽然能对分析 TFT 器件起到简化的作用并得到一些结论，却忽略了晶界和陷阱的分离特性给器件性能带来的独特影响，本论文将在第三章对此情况进行分析。

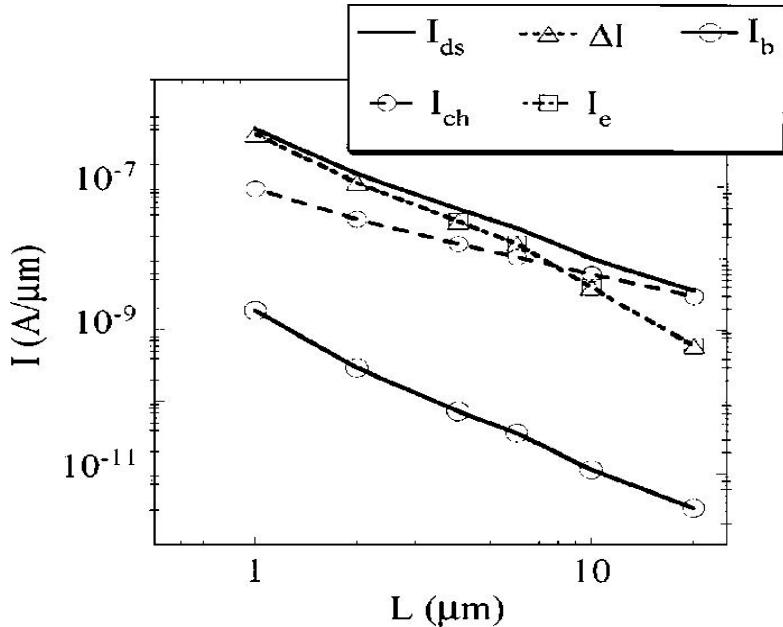

Hack 等人对 TFT 和 SOI KINK 效应的异同做了分析，他们论证到 Poly-Si TFT 器件之所以与 SOI 相比有较大的 KINK 效应是因为其空间电荷分布主要由陷阱电荷而非自由电荷决定。如图 2-11 左所示，相比于没有陷阱分布的 SOI 器件，Poly-Si TFT 器件更容易发生 KINK 效应，如图 2-11 右所示，当电子与空穴的截获横截面之比 C 增大时，更多的自由空穴将引进更多的电子使得电流更大。然而，Hack 等人的这一分析没有考虑寄生晶体管的影响。

图 2-11 SOI 和 TFT KINK 效应的区别及其受截获横截面之比的影响<sup>[37]</sup>

Armstrong 等人则指出 Poly-Si TFT 的 KINK 效应虽然与 SOI 器件有相似之处，但也有很大不同。如图 2-12 所示，Poly-Si TFT 器件的 KINK 效应受沟长影响很大，随着沟长的减小，KINK 效应显著增加，但 SOI 器件则不同，其 KINK 效应的行为几乎不受沟长的影响。Armstrong 等人从电场的角度试图对此作一解释，如图 2-13 所示，他们指出，这主要是因为 KINK 效应主要受到漏端附近电场强度的影响，SOI 器件在此处的电场强度在很大范围内几乎与沟长无关，只取决于掺杂浓度。而 TFT 器件空间电荷取决于被填充的陷阱，当沟长变化时，用于填充陷阱的电子浓度改变，因此其 KINK 效应受沟长影响很大。与此同时，他们还指出，由于 Poly-Si TFT 器件材料具有很大的陷阱浓度，所以，其体内由碰撞电离产生的空穴并不像 SOI 器件那样几乎全部被送至源端并在那里复合，而是在从漏端向源端输运的过程中逐渐复合，但这与 Valdinoci 等人的研究成果有矛盾，如前所述，Valdinoci 等人曾指出，若空穴在从漏端像源端输运的过程中逐渐复合，将不会得到与实验结果拟合的仿真结果。Armstrong 的分析同样没有考虑寄生晶体管的影响。

综上所述，分析 KINK 效应的关键之一在于对寄生晶体管机制的研究，若用传统的双极晶体管中的扩散-复合理论进行分析，将无法得到与实验和仿真结果相符的结论，如寄生晶体管的增益随漏端电压的变化。此外，沟长和陷阱对 KINK 效应的影响也需要更确切的分析和解释并需要考虑到寄生晶体管的影响。本论文将利用二维数值仿真工具，对非传统寄生晶体管机制、碰撞电离机制和 KINK 效应机制做详细的分析，以期得到更符合实际的解释，并指导实际器件设计。

图 2-12 SOI 和 TFT KINK 效应受沟长影响的差别<sup>[36]</sup>图 2-13 SOI 和 TFT 电场性质的区别及电场强度随掺杂和陷阱浓度的变化<sup>[36]</sup>

## 2.2 考虑非传统寄生晶体管性质的 KINK 效应机制

### 2.2.1 多晶硅薄膜晶体管的数值仿真

#### 利用 TCAD 工具进行数值仿真

EDA (Electronic Design Automation) 工具是当今电子系统研发的必备工具，从器件、电路到系统的研发都必须用到 EDA 工具，在电子器件研发领域，作为 EDA 工具的重要组成部分，半导体工艺和器件仿真工具 TCAD (Technology Computer Aided Design) 成为了器件研发人员的必备工具之一<sup>[38]</sup>。实际上，半导体工业的持续发展使得器件进入了纳米领域，越来越小的器件尺寸要求必须考虑越来越多的物理效应，而若用解析方法求解器件的基本方程却不得不做很多近似，这些近似越来越不能满足小尺寸器件的要求，现代计算机技术的发展使得直接求解半导体基本方程的数值模拟方法成为可能，半导体器件 TCAD 工具则应运而生。TCAD 工具可以利用一定的数值计算方法，采用合适的物理模型，结合给定的模型参数，进行计算机计算，可以模拟不同的工艺技术，指导复杂而昂贵的工艺实验，节约时间和成本；它还可以模拟不同的器件结构，得到器件的工作特性及其内部各种物理量的分布图像，并以此分析各种器件物理现象，从而调优器件性能，对器件设计进行指导。经过多年的发展与整合，如今常用的 TCAD 工具主要出自 Synopsys 和 Silvaco 这两家公司，常用的 TCAD 工具包括 Tsuprem4/Medici, Silvaco TCAD, ISE TCAD 和 Sentaurus TCAD<sup>[39]</sup>，其中，Sentaurus TCAD 集成了 Medici/Tsuprem4 和 ISE TCAD 的工艺和器件仿真的全部功能，已经成为 TCAD 的行业标准。本论文将主要使用 Sentaurus Device 工具。

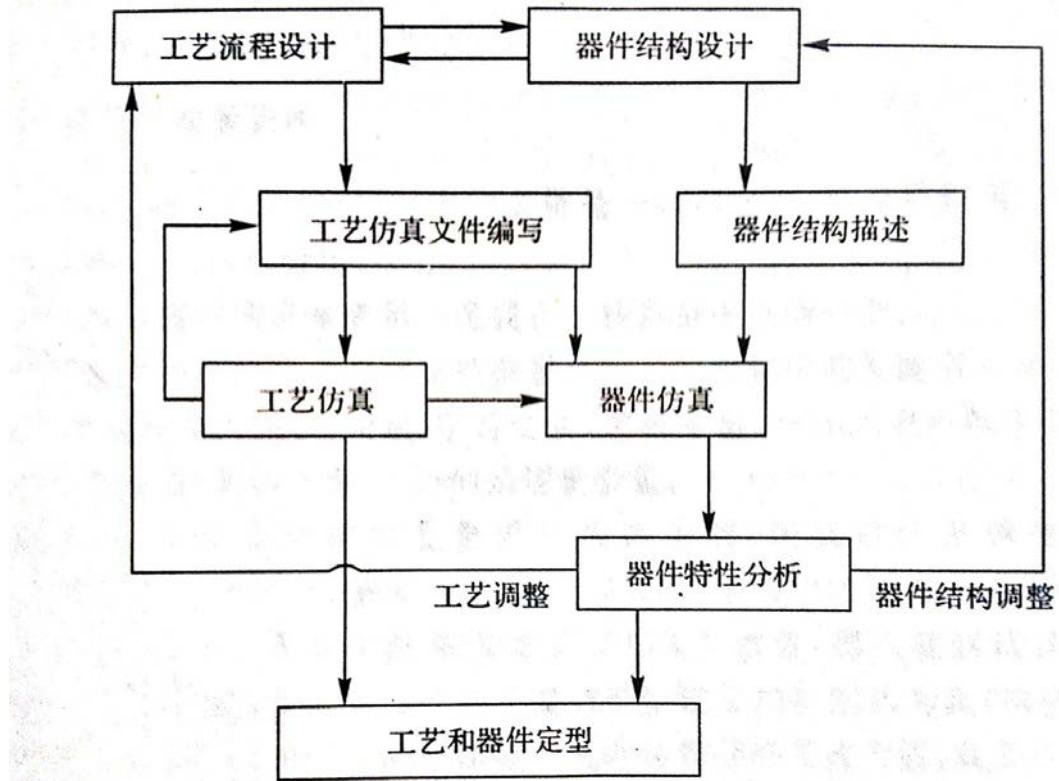

一个典型的 TCAD 设计流程如图 2-14 所示，其流程从工艺流程设计和器件结构设计出发，经过反复仿真和调优，确定最终的工艺和器件方案。在仿真过程中，需要不断的修改仿真文件以保证仿真的进行。工艺仿真和器件仿真相互联系和影响，实际使用中，也可以单独对某项工艺或某种器件进行仿真，本章将对 Poly-Si TFT 器件进行器件仿真。在对器件进行仿真时，Sentaurus Device 可以通过 Workbench 平台来完成。此平台可以使用如图 2-15 和 2-16 所示的 Sentaurus Structure Editor (SentaurusSE) 和 Sentaurus Device (SentaurusD) 工具分别对器件的结构和物理模型及参数进行编辑和仿真。以下，我们将以此对具体的 Poly-Si TFT 器件进行仿真，得到器件内部的物理量分布并进行分析。

图 2-14 典型的 TCAD 设计流程<sup>[38]</sup>

|   | Lg | Ls1  | Ls2 | tox | tsi  | tsub | pbody | nsource |

|---|----|------|-----|-----|------|------|-------|---------|

| 1 | -- | 0.25 | 0.1 | 0.2 | 0.04 | 0.04 | 0.4   | 1.5e17  |

| 2 |    |      |     |     |      |      |       | 1e20    |

图 2-15 Sentaurus Device 中 Workbench 平台的 SentaurusSE 工具

| denergy | aenergy | dconc | aconc | Xnd   | Xpd   | Xna   | Xpa   | Vg  | Vd     |

|---------|---------|-------|-------|-------|-------|-------|-------|-----|--------|

| 0.15    | 0.15    | 2e13  | 2e13  | 1e-15 | 1e-17 | 1e-17 | 1e-15 | 2.1 | 3<br>5 |

图 2-16 Sentaurus Device 中 Workbench 平台的 SentaurusD 工具

首先，我们来建立 Poly-Si TFT 器件的结构。这里有一个关键问题，就是对 Poly-Si 晶界的处理。一般有两种处理方法，一种是如前所述的有效中介近似方法，即把晶界上的陷阱近似的均匀分布在整個 Poly-Si 薄膜中，这种方法可以大大简化仿真过程，得到关键结论，但是无法得到分离的晶界对器件性能的独特影响，同时只对长沟道小晶粒的器件有效。对于短沟道大晶粒的器件，为得到更准确的结果，必须考虑晶界的离散效应。为进一步研究晶界的影响，我们将采用另一种方法，即认为陷阱只分布在晶界处，而在晶粒内部不存在陷阱，我们在这里称其为分离晶界方法（Discrete Grain Boundary, DGB），这种方法尽管加大了仿真难度，但是同时可以得到更好的精度（将在仿真结果处看到）以及可以得到晶界对器件性能的影响等（将在下一章看到）。

我们以沟长为  $1\mu\text{m}$  的 N 沟道 Poly-Si TFT 器件为例，其栅氧层厚度为  $t_{\text{ox}}=40\text{nm}$ ，硅膜厚度为  $t_{\text{si}}=40\text{nm}$ ，Poly-Si 薄膜掺杂浓度为  $1.5 \times 10^{17}\text{cm}^{-3}$ ，令其晶粒宽度为  $250\text{nm}$ ，则 1 微米长的 Poly-Si 薄膜中将有 4 个晶粒和 3 个晶界。我们将按此参数编写结构文档，以便利用 SentaurusSE 仿真其结构。首先是对几何体的描述，我们选择硅膜左上顶点为  $(0,0)$  点， $x$  轴方向由源端指向漏端， $y$  轴方向由栅极指向衬底，则可以用下面的语句描述第一个硅晶粒：

```

;structure

(sdegeo:create-rectangle (position 0.0 0.0 0.0) (position @Lg@ @tsi@ 0.0 ) "Silicon"

"body1" )

```

其中  $@Lg@$  和  $@tsi@$  为在 workbench 中输入的晶粒尺寸和硅膜厚度参数，如图 2-15 所示。类似的，可以得到其他晶粒和几何体的描述。接着我们需要定义源、漏、栅和衬底四个电极，以栅电极为例，以下语句可以实现这一功能：

```

;contacts

(sdegeo:define-contact-set "g" 4 (color:rgb 1 0 0) "##")

(sdegeo:define-2d-contact (find-edge-id(position(* @Lg@ 2)(- 0 @tox@ ) 0)) "g")

```

接着，我们需要对材料的掺杂进行描述，以下语句以第一个晶粒为例，其硼掺杂

浓度为@pbody@:

```

;profiles

(sdedr:define-constant-profile "CPD_body1" "BoronActiveConcentration" @pbody@)

(sdedr:define-constant-profile-region "Placement_body1" "CPD_body1" "body1")

```

最后，需要进行关键的网格划分，这依靠仿真人员对器件物理的熟悉程度和反复调试，不合适的网格划分可能会使得仿真结果与实际情况相差甚远或者使计算机无法进行仿真。一般来说，网格稍密会导致更精确的仿真结果和更慢的仿真速度，网格稍松会导致更快的仿真速度和精度更差的仿真结果，在物理量变化明显的地方网格稍密，如载流子浓度高处，PN 结处等。需要注意的是对于最靠近漏端的晶粒的处理。实际操作中可以发现此晶粒的网格必须较密才能得到较好的仿真精度，但过密的网格无疑会增加仿真时间。为此，我们也可以在临近漏端的硅膜处做一高度为硅膜高度，而宽度极窄的矩形区域（这一矩形的边界上将不会分布陷阱，因而不具备物理功能），从而有效提升仿真精度又不过分增加仿真时间。以下语句对第一个晶粒进行了最小尺寸为( $L_g/100, t_{si}/100$ )，最大尺寸为( $L_g/50, t_{si}/10$ )的网格划分。当相邻的网格尺寸不一样时，会发生在规定范围内的尺寸的过渡。

```

;mesh

(sdedr:define-refinement-size "RefinementDefinition_body1" (/ @Lg@ 50) (/ @tsi@ 10) (/ @Lg@ 100) (/ @tsi@ 100))

(sdedr:define-refinement-region "RefPla_body1" "RefinementDefinition_body1"

"body1")

(sde:build-mesh "mesh" "-s" "n@node @_msh")

```

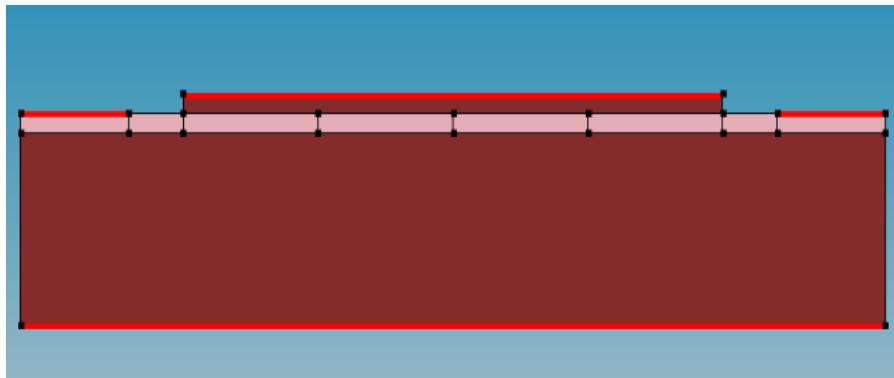

按照如上的结构文件的编辑方法和如图 2-15 所示的器件参数，可以得到如图 2-17 所示的结构仿真结果。在栅、源、漏和衬底的边界处可以看到定义的电极，源或漏电极并没有覆盖整个源或漏表面<sup>[23]</sup>。在硅薄膜层中等距分布着分离的晶界，即采用了分离晶界方法。

图 2-17 经过 SentaurusSE 工具仿真的 Poly-Si TFT 器件

在得到经过 SentaurusSE 工具仿真的 Poly-Si TFT 器件结构之后，我们需要使用 SentaurusD 工具对器件进行器件物理仿真，这需要编写器件仿真文档。该文档结合结构仿真的结果使用，并使用模型库和参数库。一般的器件文档内容包括 File 部分、Electrode 部分、Physics 部分、Plot 部分以及 Math 和 Solve 部分等。其中 File 部分规定了输入（Grid/Parameter/Doping 等）和输出文件（Plot/Current/Output 等）；Electrode 部分描述了仿真中将使用的源/漏/栅/衬底电压；Plot 部分将指定需要得到的器件内部的物理量分布（eDensity / hDensity/ eCurrent/hCurrent/Potential/SpaceCharge/AvalancheGeneration/ElectricField/Doping/eTrappedCharge/hTrappedCharge/SRHRecombination 等），使用 CurrentPlot 还可以得到指定区域内的物理量分布；Math 和 Solve 部分将指定计算机的数值求解方法（迭代次数/收敛标准/耦合方程/扫描步长和增量等）；最为关键的为 Physics 部分，它描述了对器件内的物理情况的考虑，对于 Poly-Si TFT，本论文中 Physics 部分的内容主要包括对迁移率的描述，对产生复合的描述以及对陷阱的描述等，详述如下。

### 数值仿真中物理模型的选择

Sentaurus Device 中包含了丰富的模型<sup>[39]</sup>，以适应纳米时代小尺寸器件对模型精度的要求，对于 Poly-Si TFT 来说，迁移率模型描述了载流子受到杂质散射、速度饱和和界面散射等效应的影响，影响着电流传输；产生复合模型描述了 SRH 复合作用以及碰撞电离效应，对 KINK 效应的影响至关重要，事实上，如果没有碰撞电离效应，就不会有体-源 PN 结的打开，便不会有寄生晶体管的种种影响；

陷阱模型则直接和 Poly-Si 中的晶界影响相关。下面将具体说明本论文对相关模型的选择。

**迁移率模型：**迁移率可能受到杂质、界面以及强电场等多方面影响，根据 Matthiessen 定律，各方面迁移率将以如下方式整合起来：

$$\frac{1}{\mu} = \frac{1}{\mu_{b1}} + \frac{1}{\mu_{b2}} + \dots + \frac{1}{\mu_{s1}} + \frac{1}{\mu_{s2}} + \dots \quad (2-1)$$

其中， $\mu_{b1}, \mu_{b2} \dots$  为体迁移率， $\mu_{s1} \mu_{s2}$  为表面迁移率，若电场强度较大，则在此计算结果的基础上，还必须考虑速度饱和等效应。本论文选择的的迁移率模型为：

```

Physics{ Mobility (DopingDependence eHighFieldSaturation hHighFieldSaturation

Enormal) }

```

DopingDependence 描述了杂质散射迁移率，对于 Si 材料，其默认模型为 Masetti 模型，其中，低掺杂常数迁移率  $\mu_{\text{const}}$  仅考虑声子散射，具体参数的意义和取值可以参见使用手册<sup>[39]</sup>：

$$\mu_{\text{dop}} = \mu_{\min1} \exp\left(-\frac{P_c}{N_{A,0} + N_{D,0}}\right) + \frac{\mu_{\text{const}} - \mu_{\min2}}{1 + ((N_{A,0} + N_{D,0})/C_r)^\alpha} - \frac{\mu_1}{1 + (C_s/(N_{A,0} + N_{D,0}))^\beta} \quad (2-2)$$

$$\mu_{\text{const}} = \mu_L \left(\frac{T}{300\text{K}}\right)^{-\zeta} \quad (2-3)$$

Sentaurus Device 中的器件参数放置在参数文件中，可以根据实际情况进行修改。对于 Si 材料，电子和空穴  $\mu_L$  的值分别为  $1417 \text{ cm}^2/\text{Vs}$  和  $470.5 \text{ cm}^2/\text{Vs}$ ，而对于 Poly-Si，由于其中存在大量的陷阱，其声子散射迁移率大约要小一个数量级，在本论文中，其值为  $100 \text{ cm}^2/\text{Vs}$  和  $42 \text{ cm}^2/\text{Vs}$ 。受栅极电场影响，载流子在栅氧层

和 Poly-Si 薄膜界面处会受到表面散射影响, Sentaurus Device 中有两种方法计算垂直电场, 一种是按垂直于界面计算 (Enormal), 另一种是垂直于电流 (ToCurrentEnormal), 一般来说, 两种方法所得到的结果相似, 但由于数值计算方法的问题, 一些情况下的某种方法可能会导致仿真不收敛。Enormal 选择了垂直于界面的计算方法, 其默认的 Lombardi 模型描述了界面态的声学声子散射和表面粗糙散射引起的迁移率退化<sup>[39]</sup>:

$$\mu_{ac} = \frac{B}{F_{\perp}} + \frac{C((N_{A,0} + N_{D,0})/N_0)^{\lambda}}{F_{\perp}^{1/3}(T/300\text{K})^k} \quad (2-4)$$

$$\mu_{sr} = \left( \frac{(F_{\perp}/F_{ref})^{A^*}}{\delta} + \frac{F_{\perp}^3}{\eta} \right)^{-1} \quad (2-5)$$

eHighFieldSaturation 和 hHighFieldSaturation 描述了速度饱和效应, 默认模型为如下的 Canali 模型, 其中的  $\mu_{low}$  为前述的迁移率按照 (2-1) 式联合后的结果, 默认的电场  $F_{hfs}$  计算方法为 GradQuasiFermi-静电势梯度的模, 此外电场计算方法还有 Eparallel-平行于电子电流方向的电场大小<sup>[39]</sup>:

$$\mu(F) = \frac{(\alpha + 1)\mu_{low}}{\alpha + \left[ 1 + \left( \frac{(\alpha + 1)\mu_{low}F_{hfs}}{v_{sat}} \right)^{\beta} \right]^{1/\beta}} \quad (2-6)$$

$$\beta = \beta_0 \left( \frac{T}{300\text{K}} \right)^{\beta_{exp}} \quad (2-7)$$

$$v_{sat} = v_{sat,0} \left( \frac{300\text{K}}{T} \right)^{v_{sat,exp}} \quad (2-8)$$

**产生复合模型:** 产生复合模型影响着器件中的复合电流以及碰撞电离机制, 从而对 KINK 效应产生很大影响, 本论文的产生复合模型由如下语句加入:

```

Physics{ Recombination( SRH(DopingDependence) eAvalanche(Eparallel Okuto)

```

`hAvalanche(Eparallel Okuto))}`

其中 SRH(DopingDependence) 选用了 SRH 模型并考虑了杂质对载流子寿命的影响 (Scharfetter 关系), 这些模型如 (2-9) - (2-11) 所示<sup>[39]</sup>:

$$R_{\text{net}}^{\text{SRH}} = \frac{np - n_{i,\text{eff}}^2}{\tau_p(n + n_1) + \tau_n(p + p_1)} \quad (2-9)$$

$$\tau_c = \tau_{\text{dop}} \frac{f(T)}{1 + g_c(F)}, c = n, p \quad (2-10)$$

$$\tau_{\text{dop}}(N_{A,0} + N_{D,0}) = \tau_{\min} + \frac{\tau_{\max} - \tau_{\min}}{1 + \left(\frac{N_{A,0} + N_{D,0}}{N_{\text{ref}}}\right)^{\gamma}} \quad (2-11)$$

对于碰撞电离现象, 最重要的是确立电子和空穴的碰撞电离率模型, 在此基础上, 碰撞电离产生率可以被计算出来, eAvalanche 和 hAvalanche 被用来引入碰撞电离机制。和速度饱和机制一样, 其电场的计算可以有按照静电势梯度的模来计算的 GradQuasiFermi 方法和按照平行于电子电流方向的电场大小来计算的 Eparallel 方法, 本论文在研究中发现, 对于本论文所采用的情况 Eparallel 方法可以进行正确的仿真, 而 GradQuasiFermi 方法无法完成仿真。关于碰撞电离率的模型, 其默认的模型为 van Overstraeten-de Man 模型, 但对于本论文中的情况, 研究发现采用 Okuto-Crowell 模型能得到更与实验现象相符的结论, 其模型表述为<sup>[39]</sup>:

$$\alpha(F_{\text{ava}}) = a \cdot \left(1 + c(T - T_0)\right) F_{\text{ava}}^{\gamma} \exp\left[-\left(\frac{b[1 + dT - T_0]}{F_{\text{ava}}}\right)^{\delta}\right] \quad (2-12)$$

电场  $F_{\text{ava}}$  强烈影响着碰撞电离现象的发生。本论文暂不考虑温度效应。

**陷阱模型:** Poly-Si 材料中的陷阱问题是一个复杂而重要的问题。正如前所述, 首先, 陷阱可以被近似的认为平均分布在整个 Poly-Si 薄膜中, 然而这只适用于长沟小晶粒器件, 而且无法预测晶界的分离性质所带来的影响且不够精确。本论文所进行的仿真中, 陷阱只分布在晶界上, 即为二维面分布。其次, 陷阱有施主

陷阱和受主陷阱之分，借鉴于前人的经验，本论文最终选择使用一个在能带上方的受主陷阱和一个分布在能带下方的施主陷阱。最后，陷阱能级的分布类型多种多样，常见的有指数分布和单能级分布，本论文两种方法都进行了尝试，在本章中将使用单能级分布的陷阱，指数分布的情况将在下一章中进行讨论。需要指出的是，为了拟合实验数据，必须进行仔细的参数调优，尤其是陷阱能级位置和其上陷阱浓度的值更是强烈的影响着仿真结果。经过反复调试，本论文最终选择的参数如图 2-16 中所示，施主和受主陷阱浓度均为  $2 \times 10^{13} \text{ cm}^{-2}$ ，分别与价带和导带相距  $0.15 \text{ eV}$ 。参数的意义将阐述如下。以分布在第一个晶粒和第二个晶粒之间的陷阱为例，下面的语句描述了一个分布在能带上方的距离导带 @aenergy@ 的浓度为 @aconc@ 的受主陷阱（电子和空穴的俘获横截面积分别为 @Xna@ 和 @Xpa@）和一个分布在能带下方的距离价带 @denergy@ 的浓度为 @dconc@ 的施主陷阱（电子和空穴的俘获横截面积分别为 @Xnd@ 和 @Xpd@）：

```

Physics(RegionInterface="body1/body2"){

Traps((Donor Level fromValBand Energymid=@denergy@

Conc=@dconc@ eXsection=@Xnd@ hXsection=@Xpd@)

(Acceptor Level fromCondBand Energymid=@aenergy@

Conc=@aconc@ eXsection=@Xna@ hXsection=@Xpa@))}

```

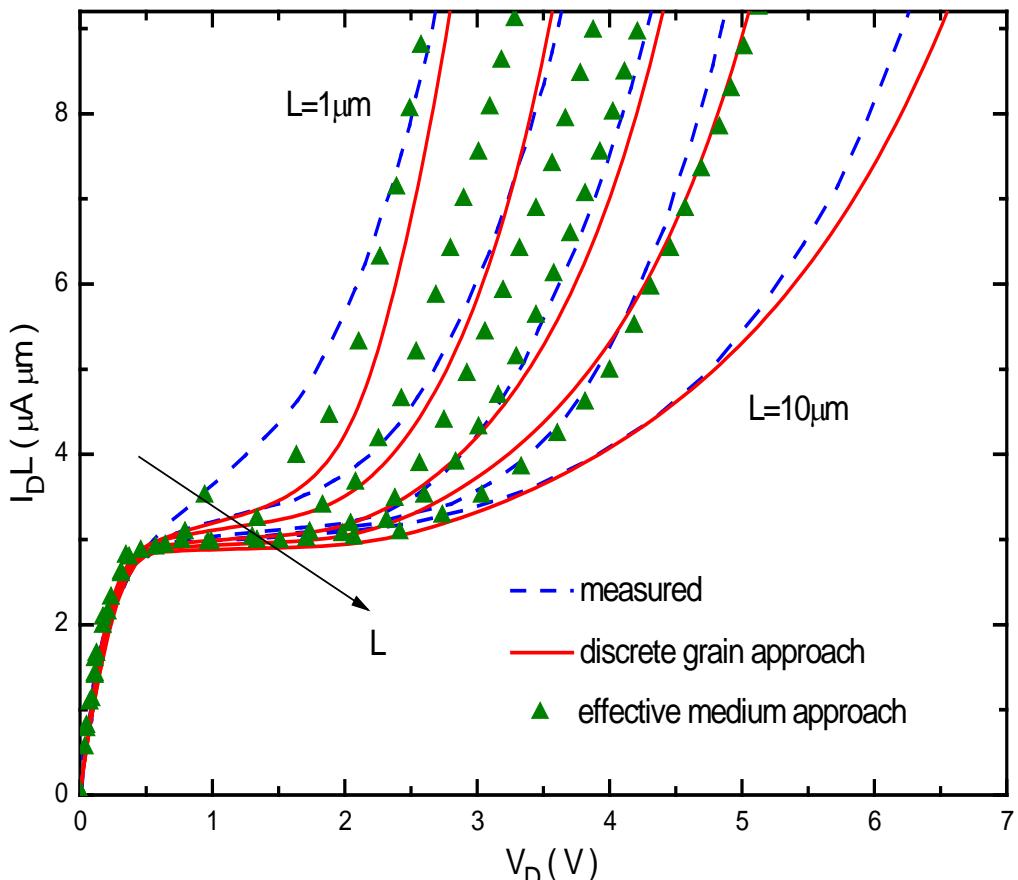

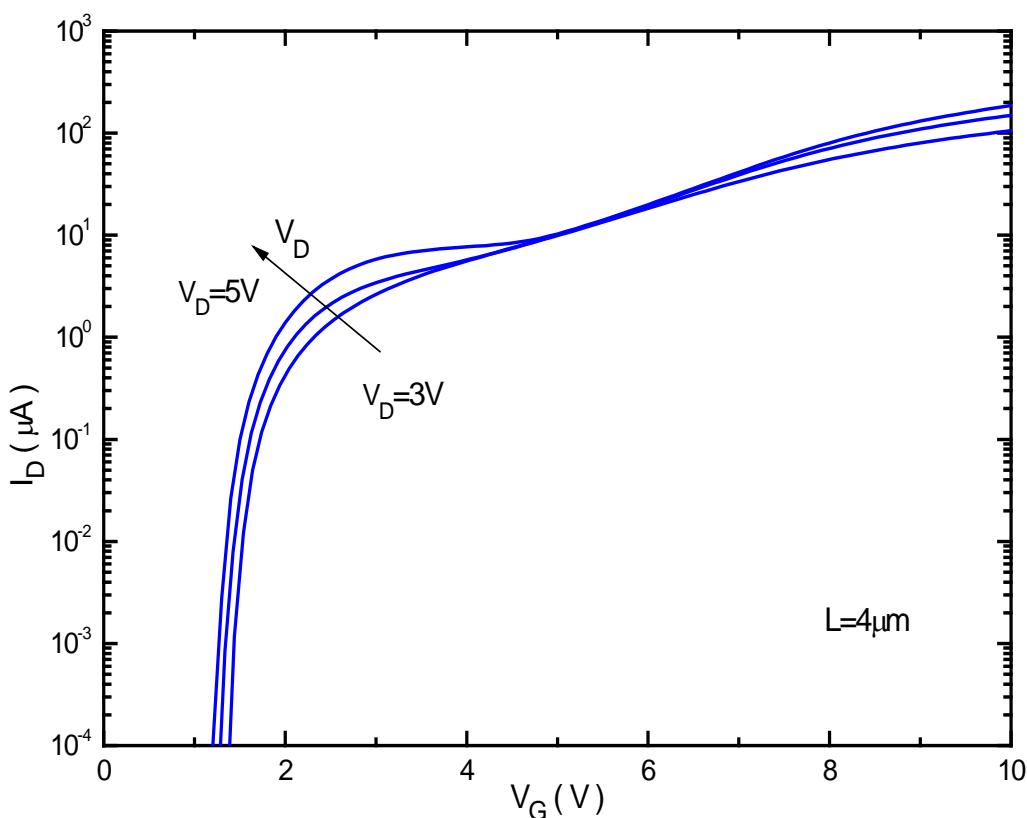

综上所述，本论文为 Poly-Si TFT 选择了调优后的常数迁移率并考虑了界面散射和速度饱和，选择了 SRH 复合模型并采用 Okuto 模型来描述碰撞电离效应，选择了分布在晶界上的单能级施主和受主陷阱并进行了仔细的调优。由此得到的仿真结果如图 2-18 所示。图中示出了沟长分别为  $1, 2, 4, 6, 10 \mu\text{m}$  的 Poly-Si TFT 的输出电流特性，所加栅电压为  $2.1 \text{ V}$ ，为器件的阈值电压，即沟道中晶粒中开始出现强反型层的电压。三组数据分别是以蓝虚线表示的实验数据，以绿色三角表示的有效中介方法所得到的仿真数据，以及本论文中以分离晶界方法得到的仿真数据。从三组数据中我们均可以看到明显的电流突增效应，且沟长越小，该效应发生的越早越强烈。更为重要的，采用分离晶界方法所得到的数据明显要好于采用有效中介近似所得到的数据，从而可以看到分离晶界方法在精度方面的优势。在短沟道  $L=1 \mu\text{m}$  时，实验数据和仿真结果的偏差可能来自器件的漏电。

图 2-18 Sentaurus Device 仿真结果-输出电流特性

### 2.2.2 非传统寄生晶体管性质及 KINK 效应机制

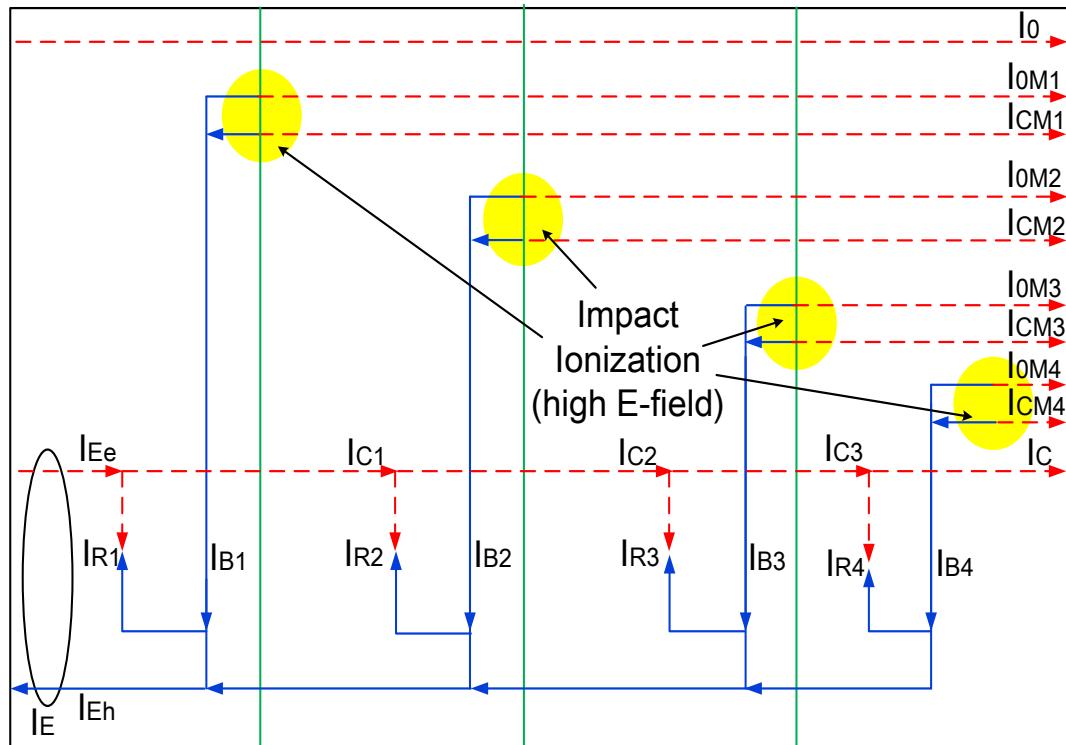

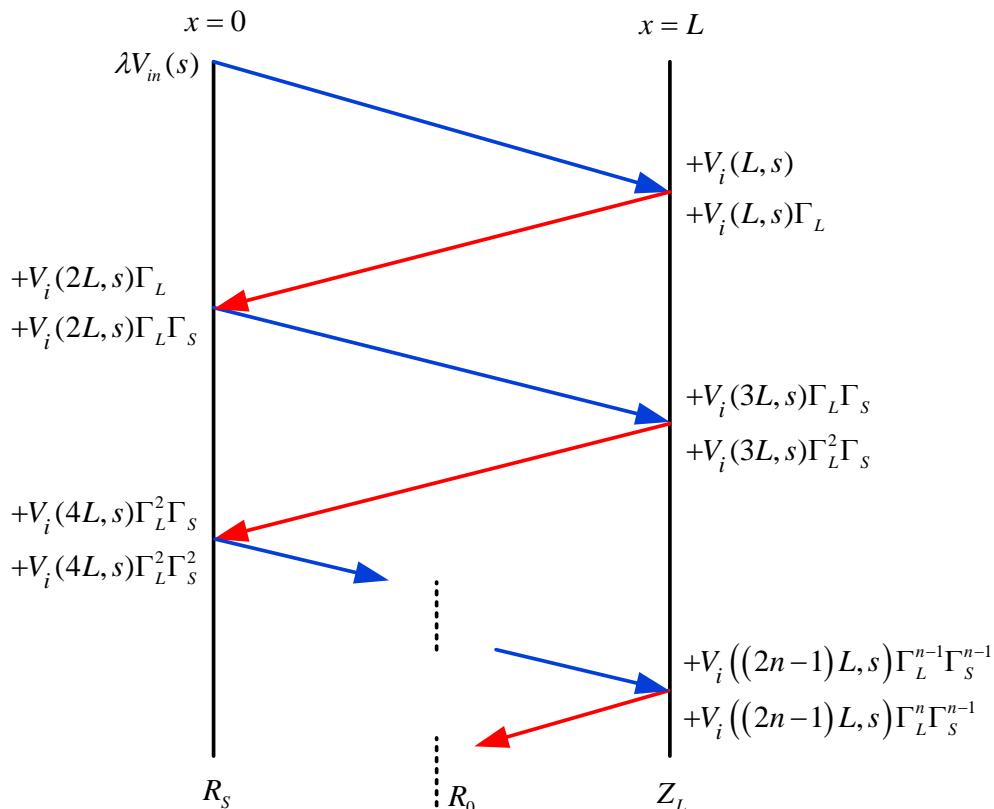

在上述 Poly-Si TFT 器件仿真结果的基础上，我们可以研究器件内部的物理图像，这一点正是仿真研究的优势所在。在此之前，我们将结合仿真结果，首先对 Poly-Si TFT 器件的 KINK 机制做初步的分析和定义。如图 2-19 所示，我们给出了包括寄生晶体管在内的 Poly-Si TFT 中的电流传导机制。如图所示，电子电流用红色虚线表示，而空穴电流用蓝色实线表示。当 Poly-Si TFT 器件工作在饱和区以后，沟道电流  $I_0$  在漏端高电场区 (high E-field) 将发生碰撞电离现象 (Impact Ionization, II)，产生大小相等的电子碰撞电离电流和空穴碰撞电离电流  $I_{0M}$ ， $I_{0M} = (M-1) I_0$ ，其中  $M$  为碰撞电离系数，碰撞电离产生的空穴将流向源端，电子流向漏端，并在碰撞电离处保持电流的连续性。Poly-Si TFT 的源端-体区-漏端构成了体区悬空的寄生晶体管，而由碰撞电离产生的到达源端的空穴抬高了寄生晶体管的体-源 PN 结电势差，当空穴积累到一定程度时，将开启体-源 PN 结，即寄生晶体管的

发射极，使得电子大量注入，并形成注入的发射极电子电流  $I_{Ee}$ 。这部分电子将向漏端进行输运，同时与空穴进行复合，并形成复合电流  $I_R$ 。到达漏端的注入的电子电流成为寄生晶体管的集电极电流  $I_C$ ， $I_C$  同样在漏端高场区发生碰撞电离，并形成碰撞电离电流  $I_{CM}$ ， $I_{CM} = (M-1) I_C$ 。 $I_{CM}$  与  $I_{OM}$  一起，构成寄生晶体管的基极空穴电流  $I_B$ ，即  $I_B = I_{CM} + I_{OM}$ ， $I_B$  包括与电子复合所形成的复合电流  $I_R$  以及到达集电极的空穴电流  $I_{Eh}$ 。 $I_{Ee}$  与  $I_{Eh}$  一起构成寄生晶体管的发射极电流  $I_E$ ， $I_E = I_{Ee} + I_{Eh}$ 。沟道电流  $I_0$ ，到达漏端的注入的集电结电子电流  $I_C$  和碰撞电离产生的电流  $I_B$  一起，构成了 Poly-Si TFT 的漏端电流  $I_D$ ，即  $I_D = I_0 + I_C + I_B$ 。对于寄生晶体管，其各个特性参数被定义为：发射极注入效率  $\gamma = I_{Ee} / I_E$ ，基区输运系数  $\alpha_t = I_C / I_{Ee}$ ，以及电流增益  $\alpha = I_C / I_E$ ， $\beta = I_C / I_B$ 。

图 2-19 考虑寄生晶体管的 Poly-Si TFT 电流传导机制

由上述分析可知，KINK 效应可以看做是碰撞电离效应和寄生晶体管效应两个关键效应的组合，碰撞电离效应和寄生晶体管效应在源端和漏端互为因果。在源端，由于碰撞电离效应所产生的空穴的堆积，寄生晶体管开启了发射极 PN 结，

并导致了电子的注入，形成了附加的电子电流，而这一电流又会在漏端发生碰撞电离。进一步分析我们可以知道，KINK 效应可以由漏电流的增量  $\Delta I = I_C + I_B$  与总漏电流  $I_D$  的比值来衡量， $\Delta I / I_D = (1+\beta) (1-1/M)$ ，可见，碰撞电离因子  $M$  和寄生晶体管电流增益  $\beta$  是决定 KINK 效应的关键因素， $M$  代表其中的碰撞电离效应，而  $\beta$  则是代表寄生晶体管工作性质的关键因素。如前所述，在 KINK 效应的研究中，如果利用传统的双极晶体管的扩散-复合的电流传导机制，无法合理解释寄生晶体管的增益  $\beta$  随漏端电压  $V_D$  的增加而减小的现象。为进一步分析 KINK 效应机制，解释这一现象并指导实际器件的分析与设计，我们将利用数值仿真结果，以分析器件内部的工作机制。

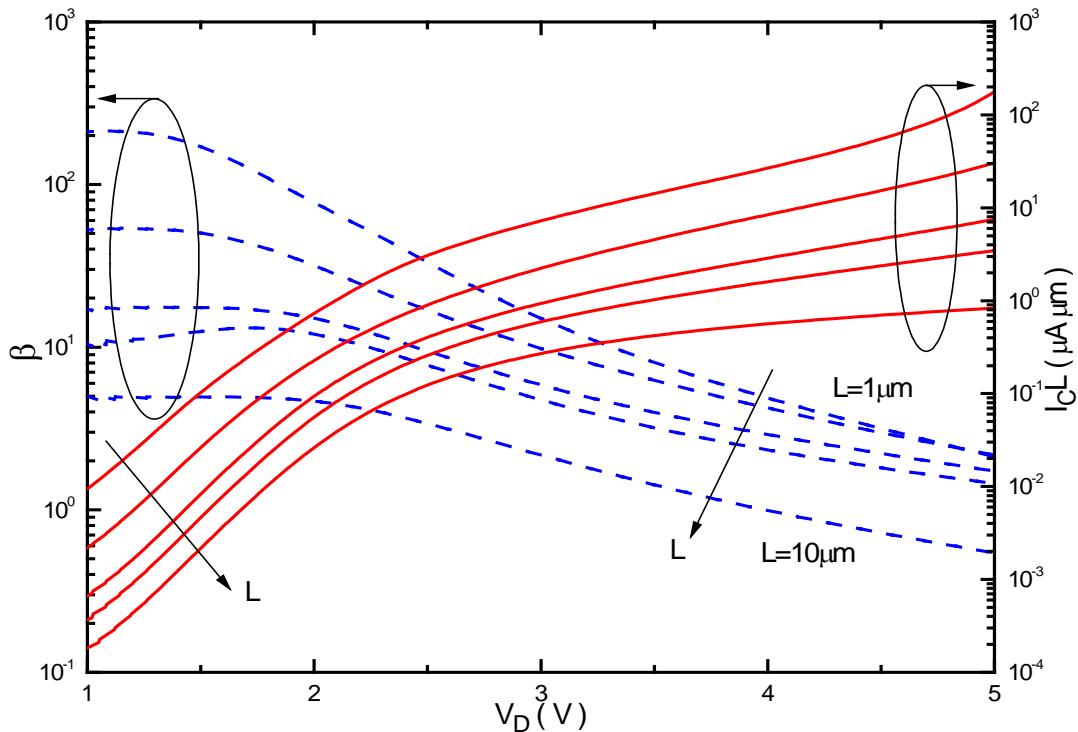

现在，我们来考虑利用上述仿真结果，做出寄生晶体管的共射极电流增益  $\beta$  和寄生晶体管集电极电流  $I_C$  随漏端电压  $V_D$  的变化曲线，并利用器件内部的物理图像，对曲线性质作解释。寄生晶体管内部各部分电流分量可以通过如下方法做出：如图 2-19 所示，首先，对于 Poly-Si TFT 器件内部的沟道电流  $I_0$ ，我们可以通过关闭碰撞电离效应后的仿真结果的器件漏电流来得到，虽然当碰撞电离开启后，这部分电流会受到 KINK 效应的影响，但这部分影响对讨论结果的影响可以忽略；其次，复合电流  $I_R$  和产生电流  $I_B$  可以通过复合率和产生率在体区的积分来得到，即  $I_R = \int q U dB$ ,  $I_B = \int q G dB$ ，其中，复合率  $U$  和产生率  $G$  可以由仿真得到；在得到  $I_0$  和  $I_B$  以后，集电极电流  $I_C$  可以通过如下的关系得到，即  $I_C = I_D - I_0 - I_B$ ，则电流增益  $\beta = I_C / I_B$  即可得到；此外，对于其他部分电流的计算方法，由于  $I_D = I_0 + I_C + I_{0M} + I_{CM} = M(I_0 + I_C) = M(I_D - I_B)$ ，故碰撞电离因子  $M = I_D / (I_D - I_B)$ ，则  $I_{0M} = (M-1) I_0$ ,  $I_{CM} = (M-1) I_C$ ；发射极电子电流  $I_{Ee}$  以及总电流  $I_E$  则为  $I_{Ee} = I_C + I_R$  以及  $I_E = I_D - I_0$ ，则发射极注入效率  $\gamma$ ，基区传输因子  $\alpha_t$  和共基极电流增益  $\alpha$  可以得到，即  $\gamma = I_{Ee} / I_E$ ,  $\alpha_t = I_C / I_{Ee}$ ,  $\alpha = I_C / I_E$ 。因为  $\beta = \alpha / (1 - \alpha)$ ,  $\alpha = \gamma \alpha_t$ ，故对于共射极电流增益  $\beta$  的研究可以通过对发射极注入效率  $\gamma$  和受复合效应影响的基区传输系数  $\alpha_t$  来进行。由上述方法可以得到如图 2-20 所示的共射极增益  $\beta$  和集电极电流  $I_{cL}$  随漏电压的电流变化曲线，如图所示，沟长越短其增益和电流越大，KINK 效应越严重，而随着漏端电压的增加，增益将变小，而集电极电流的斜率也会减小。如前所述，寄生晶体管的电流增益的此种变化与传统双极晶体管正好相反，因此，为解释这一现象，必须考虑寄生晶体管独特的电流传导机制。

图 2-20 寄生晶体管中的共射极增益  $\beta$  和集电极电流  $I_{CL}$  随漏电压的电流变化曲线，图中列出了沟长分别为  $1, 2, 4, 6, 10 \mu\text{m}$  的情况

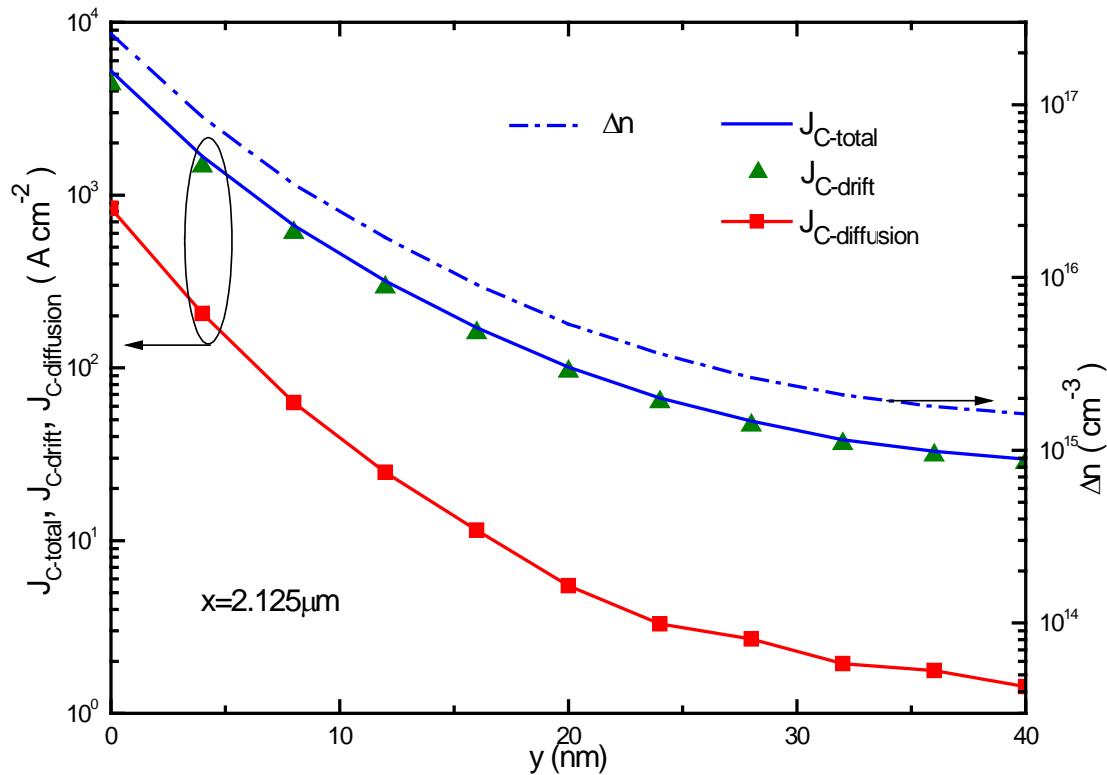

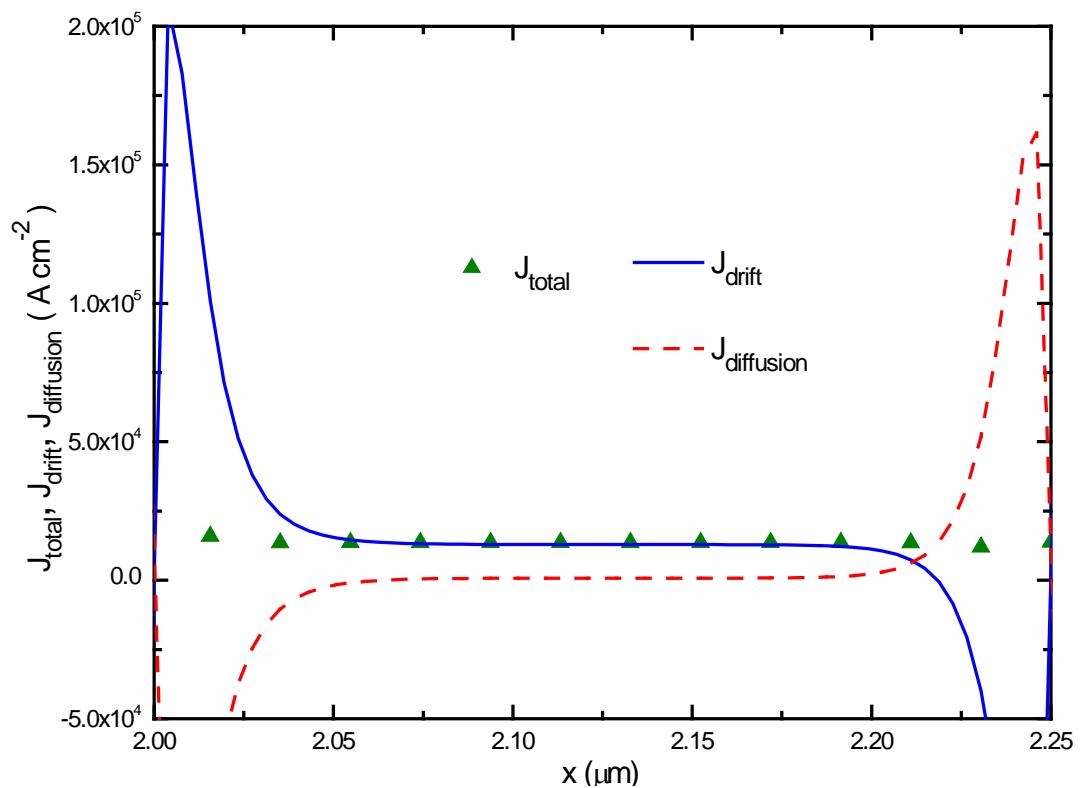

我们知道，在一般的双极晶体管中，电流主要是由少数载流子的扩散和复合所决定的。但在寄生晶体管中，这一情况发生了变化。以沟长为  $4\mu\text{m}$  的器件为例，如图 2-21 所示，在一个晶粒的内部，以  $x=2.125\mu\text{m}$  处为例，图中画出了寄生晶体管中注入的电子浓度、漂移电流密度、扩散电流密度和总电流密度的垂直分布情况，其中栅极电压  $V_G=2.1\text{V}$ ，漏极电压  $V_D=5\text{V}$ 。可以看到，注入的电子将在栅极电压的作用下，主要集中在沟道表面运动，并在源漏电场的作用下主要做漂移运动，它们是注入电子电流的主要形成成分，故注入电子电流密度的主要成分是漂移电流密度而不是扩散电流密度。另一方面，在 Poly-Si 膜下方的注入电子很少，但对于 Poly-Si 膜很薄的全耗尽器件，当漏极电压达到可以发生碰撞电离现象并开启源体 PN 结的大小时，其在 Poly-Si 薄膜的下方也将产生足够大的电场，使得此处注入的电子也进行以漂移机制为主要传导机制的输运。图 2-22 示出了在一个晶粒中沟道表面的电流成分的分布曲线，同样可以看到，在晶粒内部，电流的传导机制主要是漂移机制，同时，在晶界附近，电流的传导机制具有较为复杂的情况。

图 2-21 寄生晶体管中的注入电子和电子电流成分的垂直分布

图 2-22 一个晶粒中在沟道表面及晶粒附近的传导电流成分分布曲线

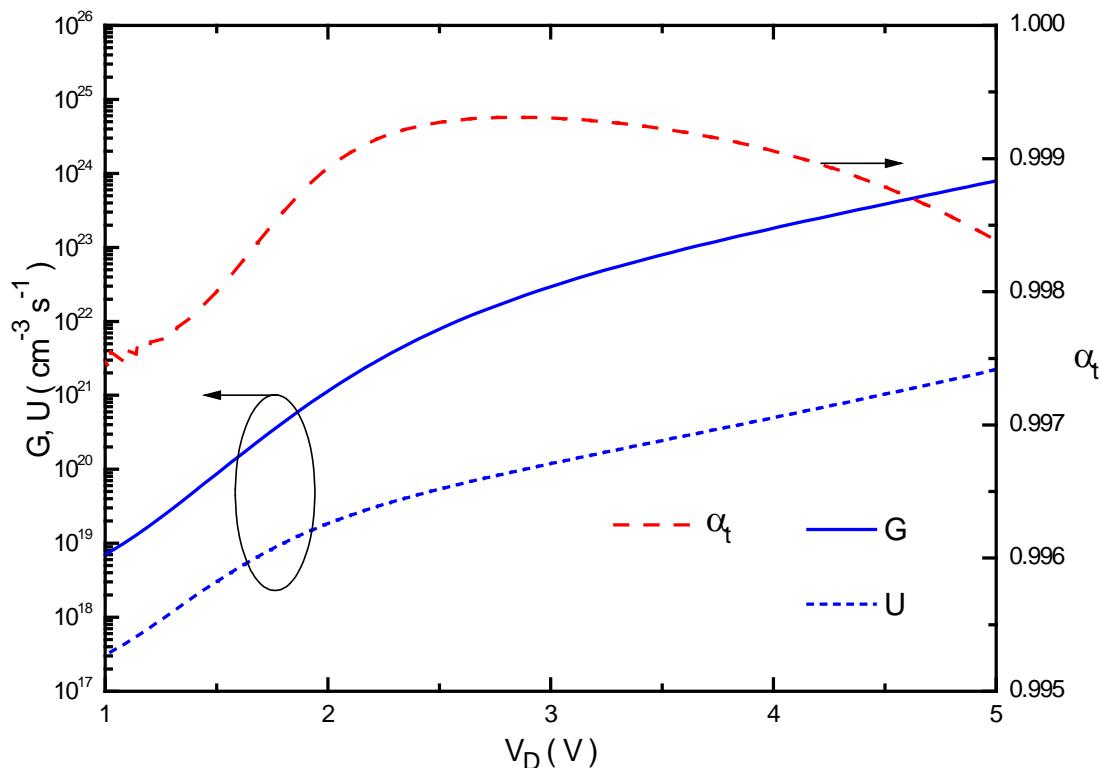

进一步的我们在图 2-23 中示出了产生率、复合率以及基区输运系数随漏端电压的变化曲线。可以看到，当漏端电压变化时，基区输运系数始终保持在 99.7% 以上，这意味着复合作用相当微弱。实际上，在发生明显的 KINK 效应时，产生率要比复合率高两个数量级，从而在 KINK 效应机制中，和碰撞电离产生的空穴电流和注入的电子电流相比，复合电流的大小可以忽略。具体的，在图 2-24 中可以看到，电流增益的下降与基区输运系数的变化基本无关，主要是由发射极注入效率的下降而引起的，从而注入电子电流中的复合电流可以忽略，同样的，空穴电流中的复合电流也可以忽略，复合机制在电流增益随漏电压的增大而下降这一现象中是可以忽略的。综上所述，我们得到了这样的结论：不同于一般的双极晶体管，寄生晶体管中的电流传导机制将以漂移机制为主，扩散和复合机制可以忽略。

基于寄生晶体管的漂移电流传导机制，现在我们来分析电流增益随漏端电压的变化情况。由上面分析可知由于复合效应可以忽略，故  $I_C = I_{Ee}$ ,  $I_B = I_{Eh}$ ,  $\beta = I_{Ee} / I_{Eh}$ ，又由于漂移电流传导机制， $\beta$  随漏端电压的变化趋势与  $\Delta Q_{BN} / Q_{BP}$  的变化趋势相同，其中， $Q_{BP}$  为 Poly-Si TFT 中的总空穴电荷，而  $\Delta Q_{BN}$  为总注入电子电荷。 $Q_{BP}$  与  $\Delta Q_{BN}$  在不同的条件下互成因果关系，首先，在源端，正是  $Q_{BP}$  的积累致使寄生晶体管开启导致了  $\Delta Q_{BN}$  的注入，此即为寄生晶体管效应；其次，在漏端，是注入的  $\Delta Q_{BN}$  和沟道电子电荷通过碰撞电离产生了  $Q_{BP}$ ，此即为碰撞电离效应。如图 2-24 所示，当漏端电压  $V_D$  增加时，碰撞电离现象逐渐产生并增强，碰撞电离系数  $M$  逐渐增大，空穴电荷  $Q_{BP}$  逐渐增加，这使得体-源电势差逐渐增大，发射结逐渐打开，电子电荷逐渐注入，注入的  $\Delta Q_{BN}$  逐渐增加，同时，考虑到碰撞电离系数  $M$  也逐渐增大，故碰撞电离产生的空穴电荷与注入电子电荷的比值  $Q_{BP} / \Delta Q_{BN}$  逐渐增大，故共射极电流增益  $\beta$  将随漏端电压的增大而逐渐减小。由此可知，碰撞电离机制和寄生晶体管的机制相互联系，在漏端电压较大时，正是碰撞电离效应的增强使寄生晶体管的增益下降。

综上所述，寄生晶体管的工作机制不是扩散复合机制，而是漂移机制。碰撞电离机制和寄生晶体管的机制相互联系，当漏端电压较大时，碰撞电离效应的增强使寄生晶体管的增益下降。KINK 效应的机制是相互联系的非传统寄生晶体管机制和碰撞电离机制的联合机制。在器件设计时必须考虑寄生晶体管的非传统性质，同时要考虑高漏端电场带来的强碰撞电离效应以及两者的关系。

图 2-23 产生率、复合率以及基区输运系数随漏端电压的变化曲线

图 2-24 基区输运系数、发射极注入效率、共基极电流增益、碰撞电离因子、注入的电子和空穴电荷随漏端电压的变化曲线

### 2.2.3 寄生晶体管中的集电极电流特性分析

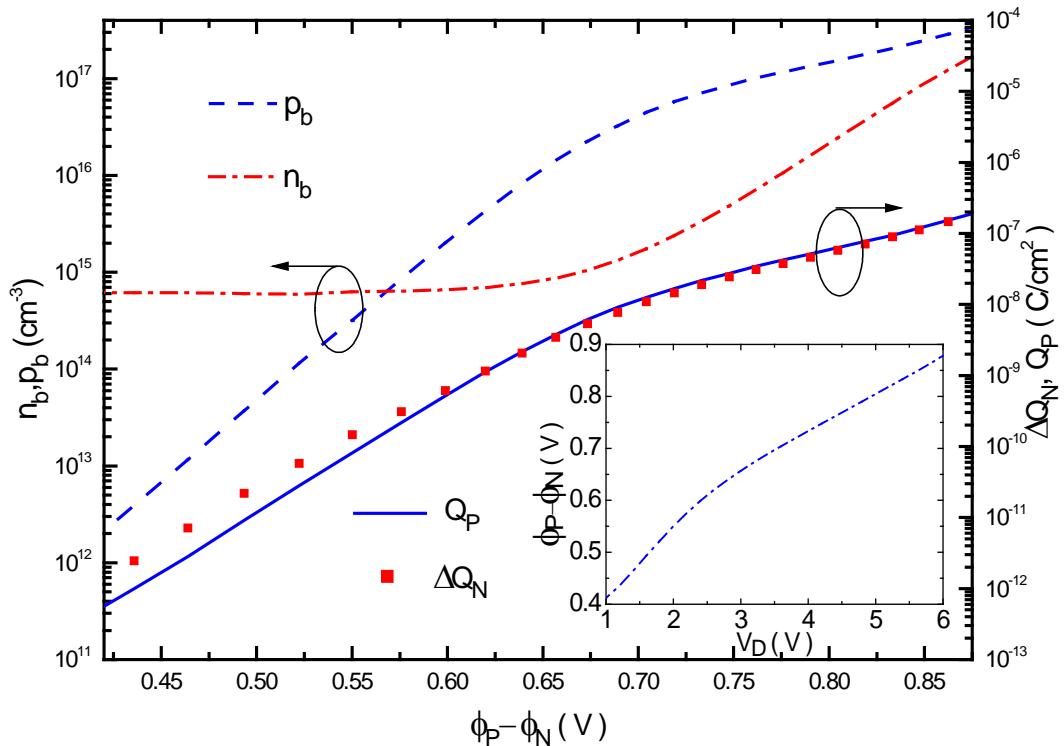

如图 2-20 所示, 寄生晶体管的集电极电流随漏端电压的变化速度会随着漏端电压的增大而减小, 这可以通过图 2-25 来理解。如图 2-25 所示, 选取 Poly-Si TFT 靠近源端的一点  $x=0.1\mu\text{m}$ ,  $y=38\text{nm}$  处, 其电子和空穴浓度分别为  $n_b$  和  $p_b$ , 他们满足关系  $n_b p_b = n_i^2 \exp(\Phi_p - \Phi_n)$ , 当漏端电压增加时, 碰撞电离产生的空穴在栅电压的作用下主要集中在 Poly-Si 下方, 故  $p_b$  随之增加, 注入的电子主要集中在 Poly-Si 上方, 故  $n_b$  基本不变, 则  $p_b$  正比于  $\exp(\Phi_p - \Phi_n)$ 。当漏端电压足够大时,  $n_b$  开始增加, 则  $p_b$  增加的速度要相应减小。因为空穴主要集中在薄膜下方, 这意味着  $x=0.1\mu\text{m}$  处的空穴面电荷的增加速度也要随之减小。考虑到近似的电中性条件, 此处注入的电子面电荷的变化趋势应与空穴面电荷相同, 故图中注入的电子电荷面密度随电势差的变化有增速减弱的现象, 这使得注入的电子电荷面密度随漏电压的增大而增速放缓。由前面的分析可知, 寄生晶体管中以漂移机制为主要的电子电流传导机制, 故集电极电流随漏端电压的增大而增速放缓, 如图 2-20 所示。

图 2-25 器件靠近源端的电子浓度和空穴浓度, 注入电子电荷和空穴电荷随准费米势差值的变化关系

## 2.3 考虑寄生晶体管性质和陷阱影响的沟长对 KINK 效应的影响机制

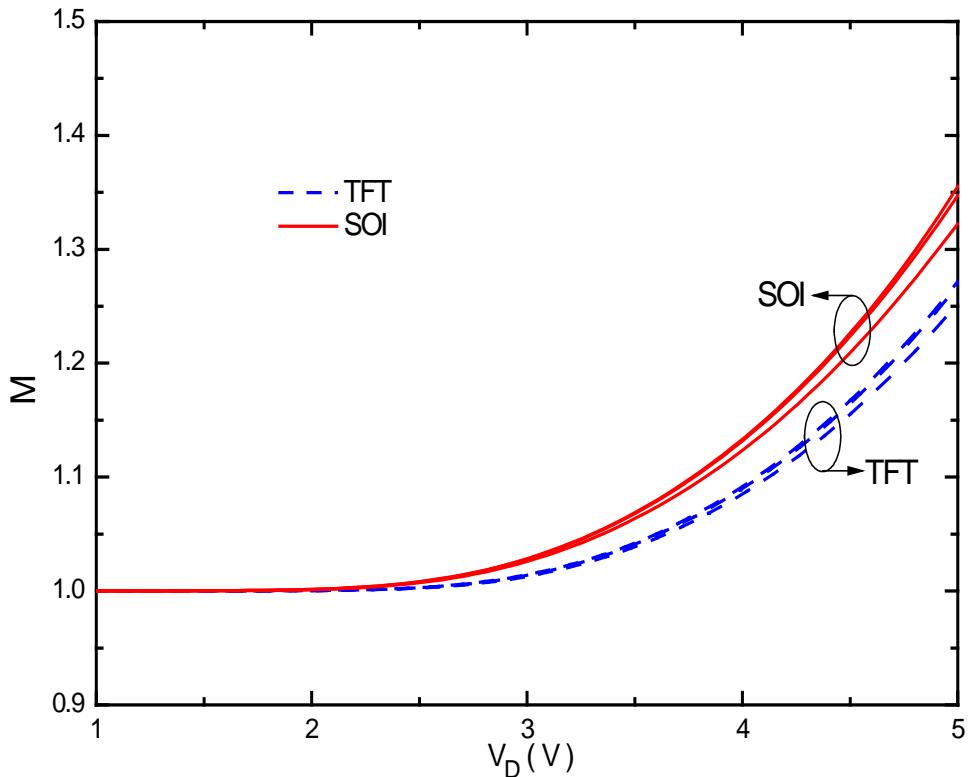

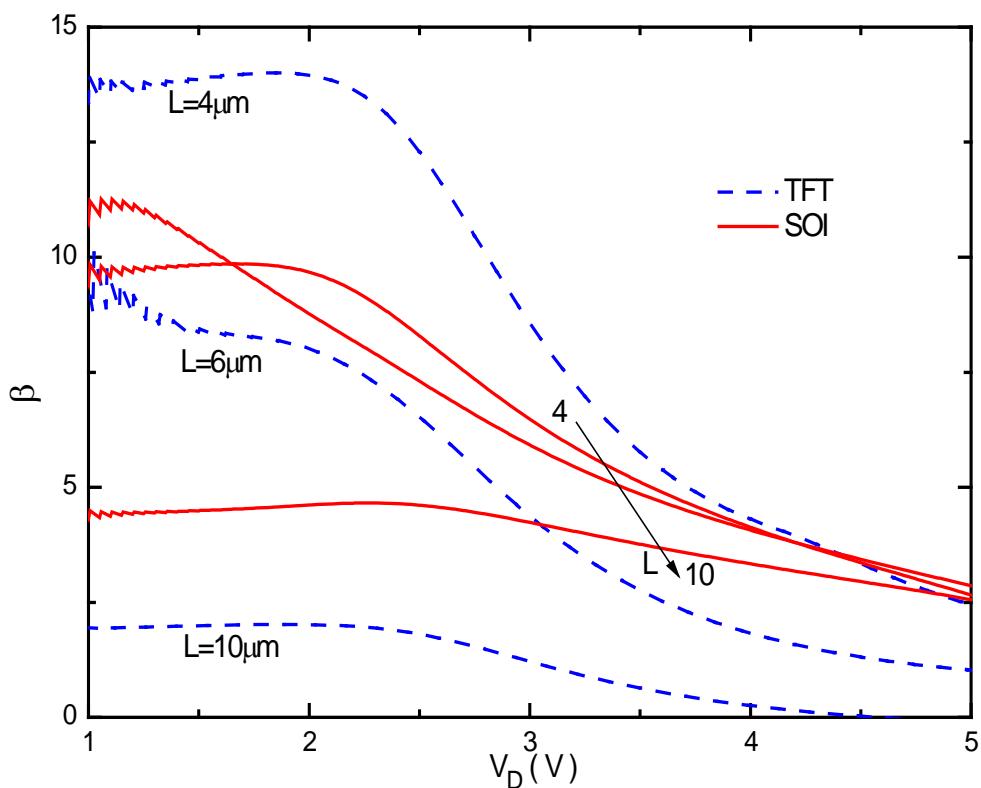

### 2.3.1 考虑寄生晶体管性质的沟长对 KINK 效应的影响机制

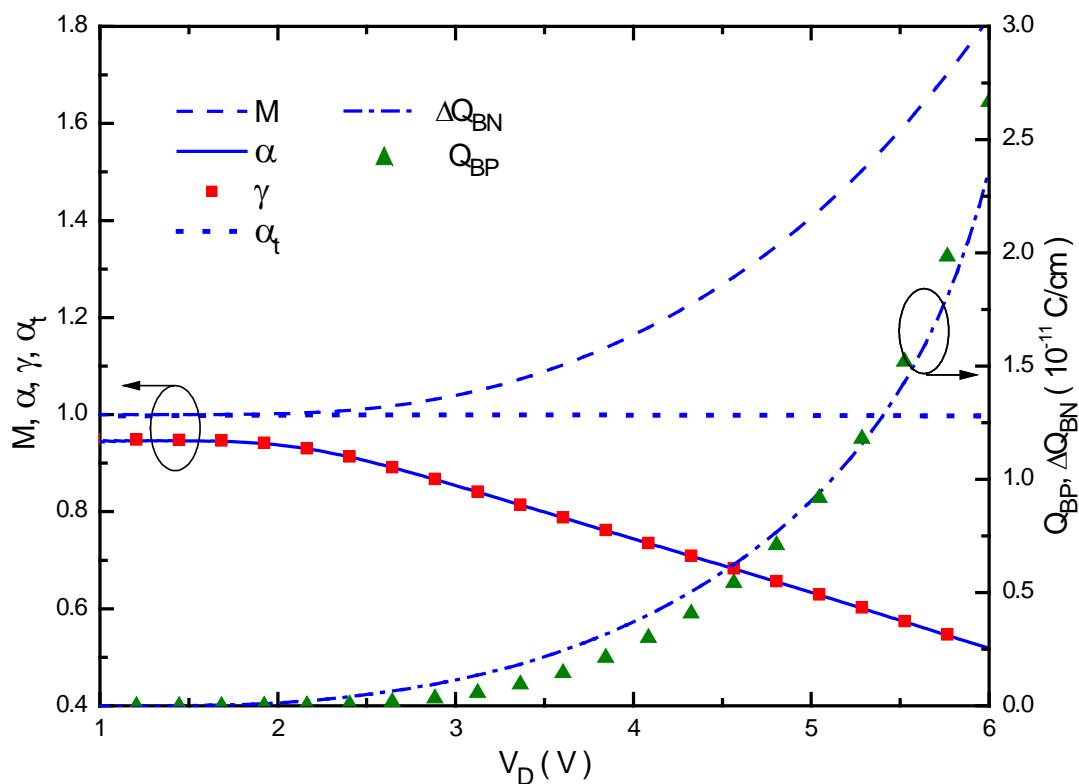

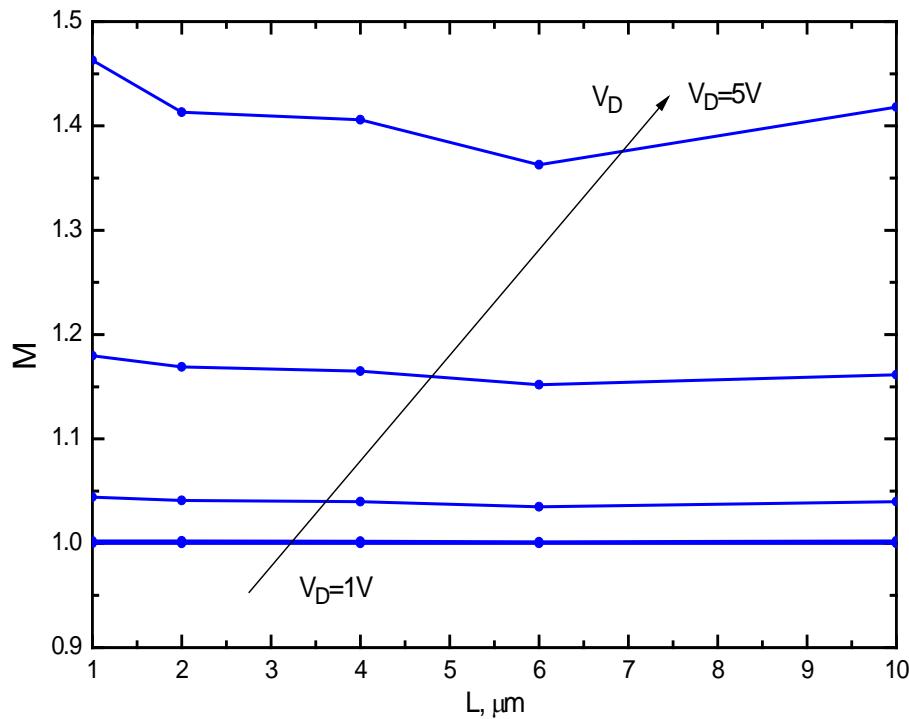

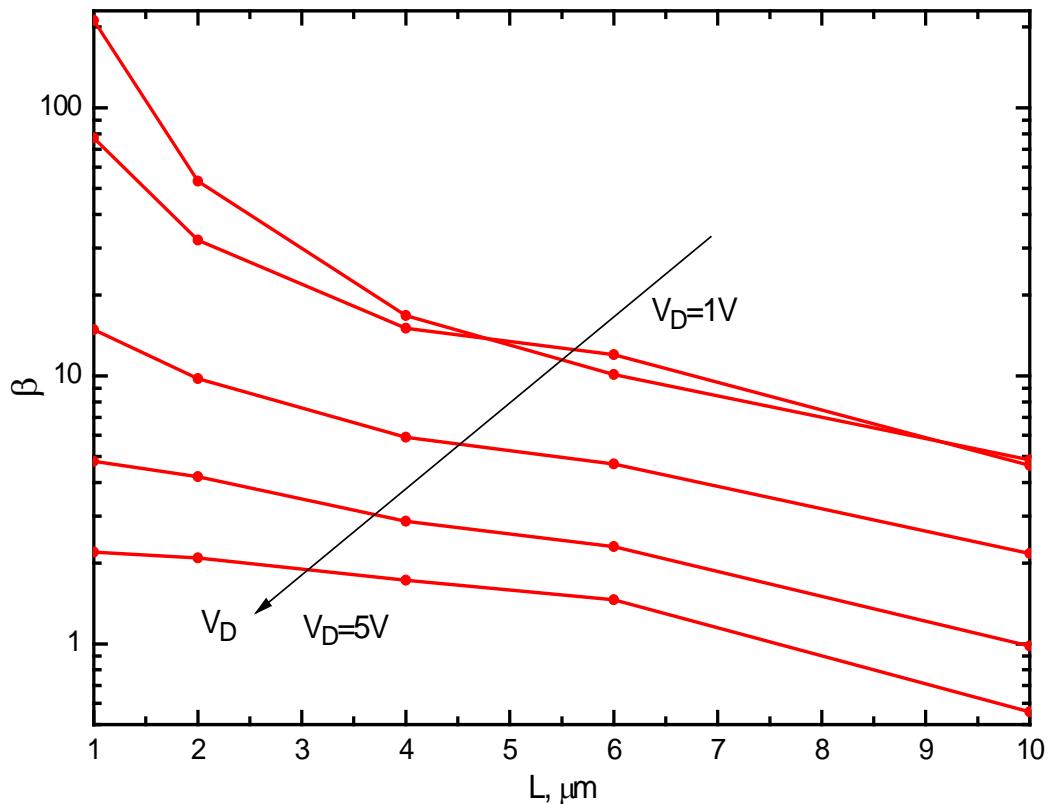

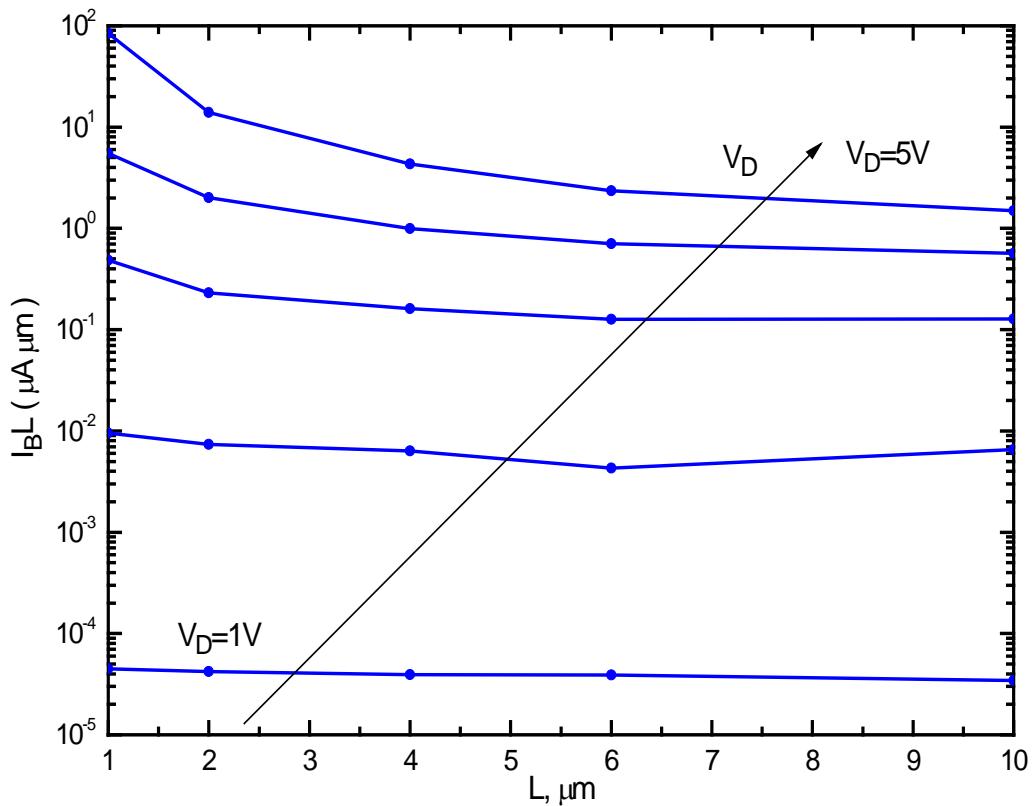

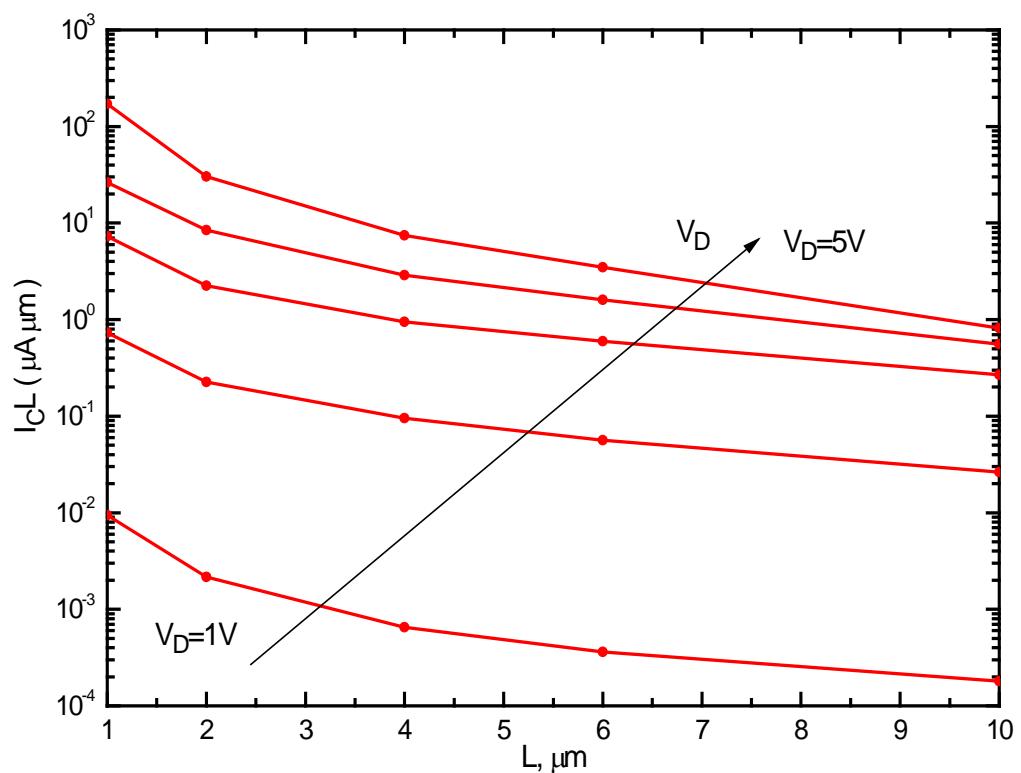

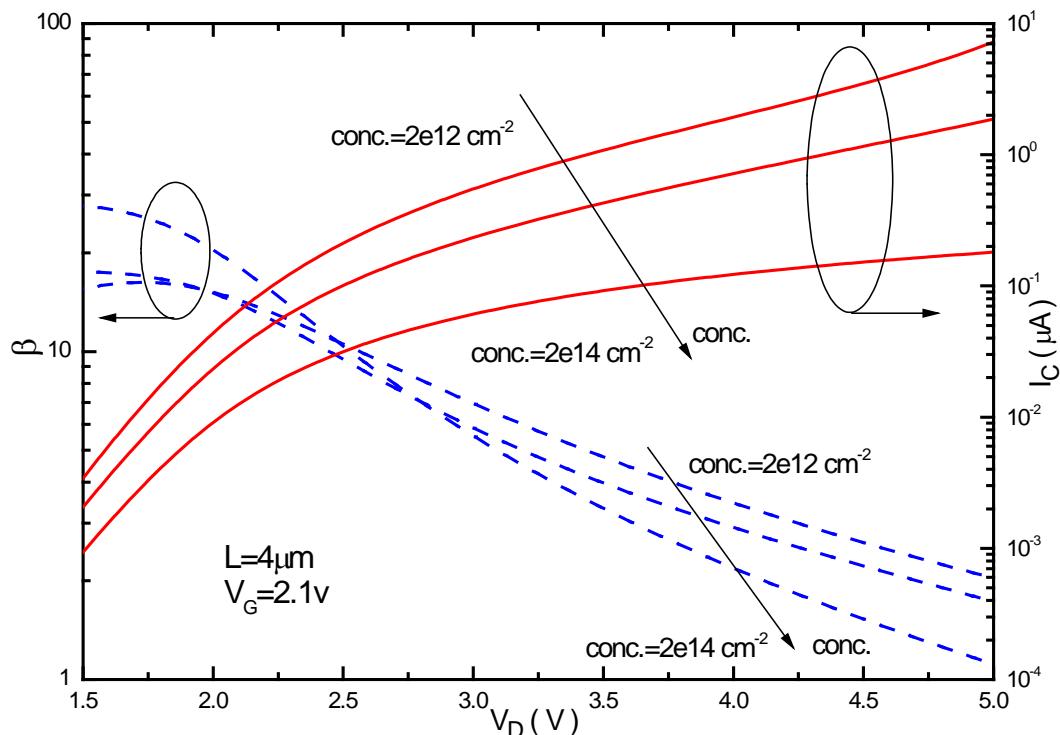

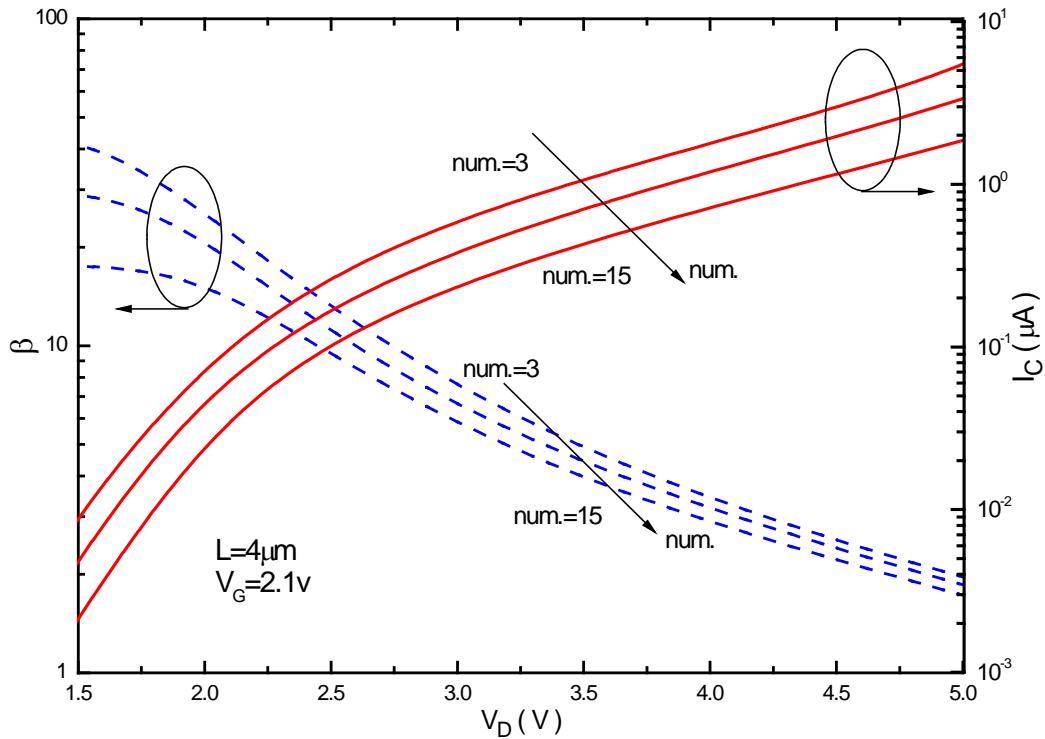

如图 2-20 所示, 沟道长度的变化对 KINK 效应也将产生影响。如前所述, 碰撞电离因子  $M$  和寄生晶体管电流增益  $\beta$  是表征 KINK 效应的两个关键因素, 可以通过研究  $M$  和  $\beta$  随沟道长度的变化来研究沟长对 KINK 效应的影响。利用前述仿真方法, 采用沟道长度  $L=1,2,4,6,10\mu\text{m}$  长度的晶体管, 图 2-26 示出了碰撞电离因子  $M$  随沟道长度的变化关系, 图 2-27 示出了寄生晶体管电流增益  $\beta$  随沟道长度的变化关系, 栅压偏置为  $V_G=2.1\text{V}$ , 漏极偏压分别为  $1,2,3,4,5\text{V}$ 。如图所示, 当漏端电压较大时, 碰撞电离因子较大而寄生晶体管增益较小, 而当漏端电压较小时, 寄生晶体管增益较大而碰撞电离因子较小, 即寄生晶体管的增益随漏端电压的增大而减小, 这和前面得到的结论一致。如图 2-26 所示, 在漏端电压较大或者较小时, 碰撞电离系数均几乎与沟道长度无关。这是因为碰撞电离因子只取决于夹断区电场的强度, 而这电场强度几乎只受漏端电压的影响, 而与沟道长度无关。由此可知, 沟道长度对 KINK 效应的影响主要是通过其对寄生晶体管的影响来进行的。

图 2-26 碰撞电离因子  $M$  随沟道长度的变化关系

如图 2-27 所示, 当漏端电压较小时, 寄生晶体管的电流增益将随沟道长度显著变化, 沟道长度越小, 寄生晶体管电流增益越大。而当漏端电压较大时, 寄生晶体管的增益几乎不随沟长变化。因为寄生晶体管共射极电流增益  $\gamma = I_C/I_B$ , 我们可以通过考察集电极电流  $I_C$  和基极电流  $I_B$  来分析这一现象。图 2-28 示出了寄生晶体管基极电流  $I_B$  随沟道长度的变化关系, 图 2-29 示出了寄生晶体管集电极电流  $I_C$  随沟道长度的变化关系, 栅压偏置为  $V_G=2.1V$ , 漏极偏压分别为  $1, 2, 3, 4, 5V$ , 沟道长度为  $1, 2, 4, 6, 10\mu m$ 。如图所示, 当漏端电压较小时, 基极电流即碰撞电离产生电流几乎不随沟道长度而变化, 而集电极电流则随沟道长度显著变化, 当沟道长度减小时, 集电极电流显著增大; 当漏端电压较大时, 基极电流和集电极电流都将随着沟道长度的变化而显著变化, 当沟道长度减小时, 它们均将增大。需要注意的是, 图中画出的曲线其纵坐标分别为  $I_B L$  和  $I_C L$ , 这样, 单纯的因为沟道长度的减小使得一般的沟道电流因为源漏电场增强而增大的现象已经被考虑进去,  $I_B L$  和  $I_C L$  曲线不会因此而有翘曲的现象,  $I_B L$  和  $I_C L$  曲线的翘曲只可能是因为寄生晶体管工作状况的改变, 这可以解释如下。

图 2-27 寄生晶体管电流增益  $\beta$  随沟道长度的变化关系

图 2-28 寄生晶体管基极电流随沟道长度的变化关系

图 2-29 寄生晶体管集电极电流随沟道长度的变化关系

图 2-30 集电极电流及其碰撞电离电流在总电流中的比例

这是因为，当沟道长度减小时，沟道电流将增加，碰撞电离电流将增加（因为图中画出的是  $I_B L$ ，故曲线值不会因为这种增加而增加），这将产生更多的碰撞电离空穴，使得堆积在源体 PN 结的空穴增多，电势差增加，寄生晶体管发射结更容易被打开，更多的电子电流将从发射极注入进来，所以集电极电流  $I_C L$  将增加，其曲线会因此而翘曲，而无论漏电压是大是小。碰撞电离电流  $I_B L$  由原沟道电流  $I_0$  和集电极电流  $I_C$  两部分电流分别发生碰撞电离而产生，即  $I_B = (M-1) I_0 + (M-1) I_C$ ，如图 2-30 所示，当漏端电压较小时，集电极电流及其碰撞电离电流  $MI_C$  在总漏端电流  $I_D = MI_0 + MI_C$  中所占的比例很低，相对于  $I_0$ ， $I_C$  可被忽略，故在漏端电压较小时，基极电流  $I_B L$  基本只受  $I_0 L$  和  $M$  值的影响， $I_B L = (M-1) I_0 L$ ，即而基本不随沟长的减小和  $I_C L$  的增加而增加；但当漏电压较大时，如图 2-30 所示，集电极电流及其碰撞电离电流  $MI_C$  在总电流中的比例将很大，故基极电流  $I_B L$  将强烈的受到  $MI_C$  的影响，随沟长的减小和  $I_C L$  的增加而增加。由此可知，当漏电压较小时，因为  $I_C L$  将随沟长的减小而增加，而  $I_B L$  基本不变，故共射极电流增益  $\beta$  将随沟长的减小而增加；而当漏电压较大时，因为  $I_C L$  和  $I_B L$  都将随沟长的减小而增加，故电流增益  $\beta$  基本不变。从本小节我们可以知道，对于沟道长度越短的器件，其 KINK 效应越大，因此对于短沟器件的设计必须充分考虑 KINK 效应。

### 2.3.2 沟长对 KINK 效应影响机制中陷阱的作用

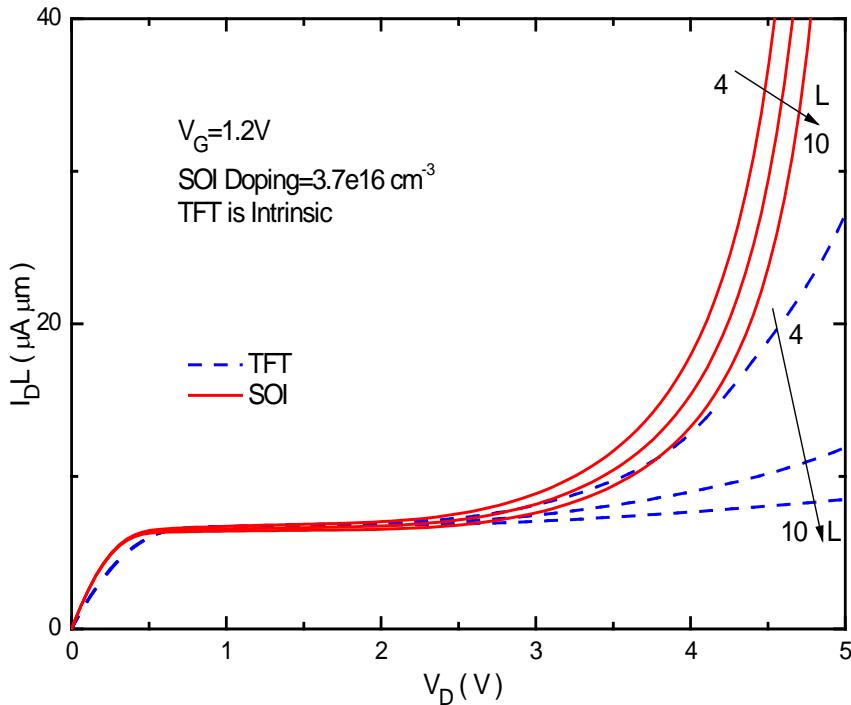

图 2-31 TFT 和 SOI 器件 KINK 效应的区别以及陷阱的影响

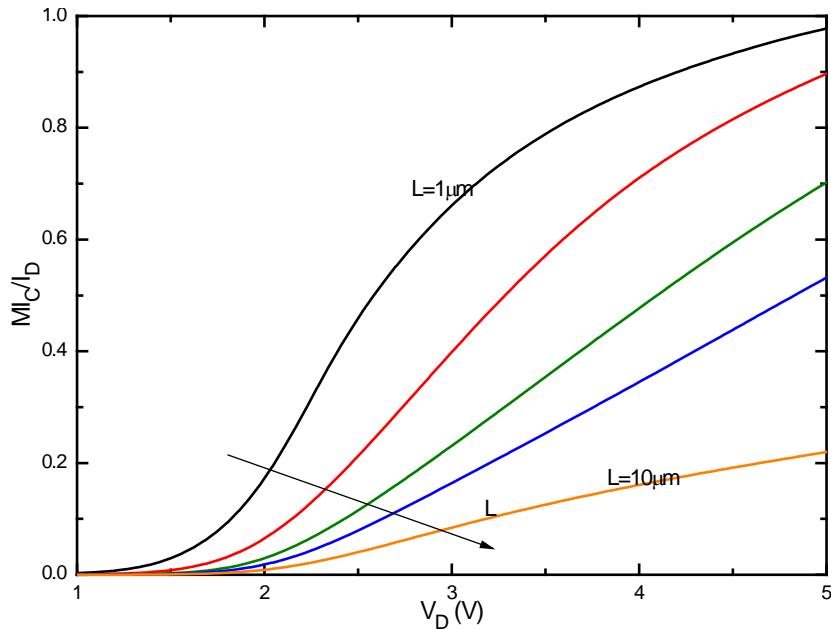

相比于 SOI 器件，Poly-Si TFT 器件最大的特点是其具有晶界结构，并且其上分布有大量陷阱，故研究陷阱给 Poly-Si TFT 器件 KINK 效应所带来的影响可以通过考察 TFT 器件与 SOI 器件的异同来进行。如图 2-31 所示，我们选取沟道长度分别为 4,6,10 $\mu\text{m}$  的 SOI 与 TFT 器件进行仿真研究，除了晶界和陷阱结构以外，其他结构一样，为保证 SOI 器件和 TFT 器件具有相仿的电流大小，SOI 器件的掺杂浓度为  $3.7 \times 10^{16} \text{ cm}^{-3}$ ，TFT 器件为本征器件，其陷阱性质与前述相同，栅压偏置为  $V_G=1.2\text{V}$ 。从图 2-31 中可以明显看到 SOI 器件与 TFT 器件 KINK 效应的区别-SOI 器件由 KINK 效应产生的电流受到沟长变化的影响较小，而 TFT 器件则较大。如前所述，表征 KINK 效应的两个关键因子是碰撞电离系数  $M$  和寄生晶体管电流增益  $\beta$ ，为研究陷阱所带来的影响，图 2-32 和图 2-33 分别画出了 TFT 和 SOI 器件中碰撞电离因子  $M$  和寄生晶体管电流增益  $\beta$  随漏端电压的变化曲线，示出了其受到的沟道长度的影响。如图 2-32 所示，TFT 和 SOI 器件中碰撞电离因子  $M$  受到的沟道长度的影响很小，这是因为两种器件中的碰撞电离现象均只取决于漏端电压的大小，陷阱和沟长对此影响很小。故陷阱对 TFT 器件 KINK 效应的影响主要通过其对寄生晶体管的性质的影响来进行。

图 2-32 TFT 和 SOI 中碰撞电离因子  $M$  受到的沟道长度的影响很小

图 2-33 TFT 和 SOI 中寄生晶体管电流增益  $\beta$  受到的沟道长度的影响很大

如图 2-33 所示，在 SOI 器件和 TFT 器件中寄生晶体管电流增益  $\beta$  都将受到沟道长度的影响，但随着漏端电压的增加，SOI 器件中沟长的影响迅速消失，而 TFT 器件则不然。这正是因为 TFT 器件中陷阱的影响。如上一节所述，当漏电压较大时，由于缩短够沟长会使得碰撞电离电流增大，从而使得电流增益随沟长的变化减弱。在 SOI 器件中，由于没有陷阱，堆积在体区的空穴随漏端电压的增大而增加的很快，所以其碰撞电离电流很快就能随着沟长变化，从而使得电流增益很快就不受沟长影响；而在 TFT 器件中，因为其陷阱上具有大量陷阱，随着漏端电压的增大，空穴电荷积累的相对很慢，故需要更大的漏端电压才能使得碰撞电离电流随沟长变化，增益不随沟长变化。故如图 2-33 所示，SOI 器件中寄生晶体管增益受沟长的影响随漏端电压的增大很快消失，而 TFT 器件则很慢，这正是导致图 2-31 中现象的原因。从本小节的分析我们可以知道，沟道长度会更强烈的影响 Poly-Si TFT 器件的 KINK 效应，故设计短沟道 Poly-Si TFT 器件时更应充分考虑 KINK 效应。

### KINK 效应研究小结

采用 Sentaurus Device TCAD 工具，本章对 Poly-Si TFT 器件做了二维数值模拟，其中对于陷阱的处理采用了分离晶界方法，提升了仿真的精度并丰富了仿真结果。利用仿真结果，本章分析了寄生晶体管的电流传导机制，首次提出寄生晶体管的电流传导机制是漂移机制而非扩散复合机制，碰撞电离机制和寄生晶体管的机制相互联系，当漏端电压较大时，碰撞电离效应的增强使寄生晶体管的增益下降，KINK 效应的机制是相互联系的非传统寄生晶体管机制和碰撞电离机制的联合机制。本章又提出 KINK 效应所受到的沟长的影响是因为寄生晶体管的性质受到了影响，而当漏电压较大时沟长的影响较弱是因为注入的大量电子使得集电极电流在总漏端电流中的比例大幅上升，从而使得碰撞电离电流随沟长而变化，进而导致电流增益基本不随沟长变化。本章还提出陷阱对 KINK 效应的影响同样是对影响寄生晶体管的工作性质来进行的，它会使得堆积在体区的空穴积累速度变慢，从而延缓了随着漏电压的增大寄生晶体管增益不随沟长变化的现象，导致在输出特性曲线中，相较于 SOI 器件，TFT 器件由于 KINK 效应所带来的电流增加更依赖于沟长的变化。本章的创新性工作提出了 KINK 效应的新机制，解释了 KINK 效应的有关现象，为进一步建立数学模型提供了基础，同时指出，在器件设计时

必须同时考虑浮体结构带来的非传统寄生晶体管效应和漏端高电场带来的强碰撞电离效应以及两者的相互作用，而对于短沟道 TFT 器件，其 KINK 效应会变得更加严重，更应该充分考虑。

## 第三章 多晶硅薄膜晶体管离散晶界效应研究

Poly-Si TFT 在结构和材料上的主要特点之一是具有晶界结构，晶界上分布有大量缺陷，这使得 Poly-Si TFT 有许多与此相关的问题<sup>[40]-[51]</sup>。当器件沟道较长、晶粒较小时，可以近似认为缺陷均匀的分布在整个 Poly-Si 薄膜之中，即采用有效中介近似方法（Effective Medium Approximation，EMA），这样做可以大大简化仿真、建模和分析，得到有用的结论；但当器件沟道较短、晶粒较大时，由于晶界数目较少，其离散特性将强烈的影响着 TFT 器件的性能，如晶界的数目、位置和其上缺陷浓度的影响，晶界附近的碰撞电离效应以及漏致势垒高度降低（Drain Induced Grain Barrier Lowering，DIGBL）效应等，这些效应被称为离散晶界效应。对于现代短沟道、大晶粒、少晶界的 Poly-Si TFT 器件来说，离散晶界效应越来越重要，本章将通过二维数值仿真和基于物理的解析建模方法，对离散晶界效应进行研究。

### 3.1 离散晶界效应简述

#### 大晶粒器件

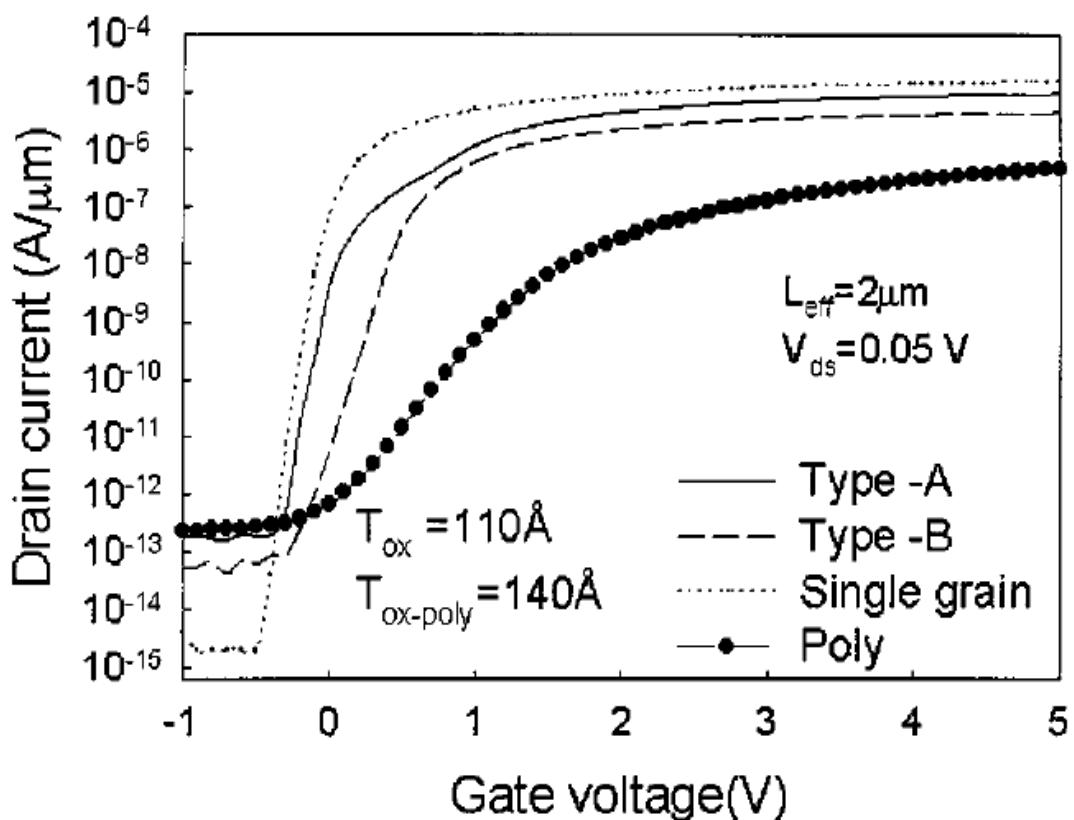

一般来说，当晶粒尺寸增大、晶界数目减小时，Poly-Si TFT 器件的性能会随之增强，器件的迁移率会提升，电流驱动能力会增强，泄漏电流会减少，亚阈值特性会变好，因而具有大晶粒尺寸、少晶界数目的 Poly-Si TFT 器件一直是研究的热点。

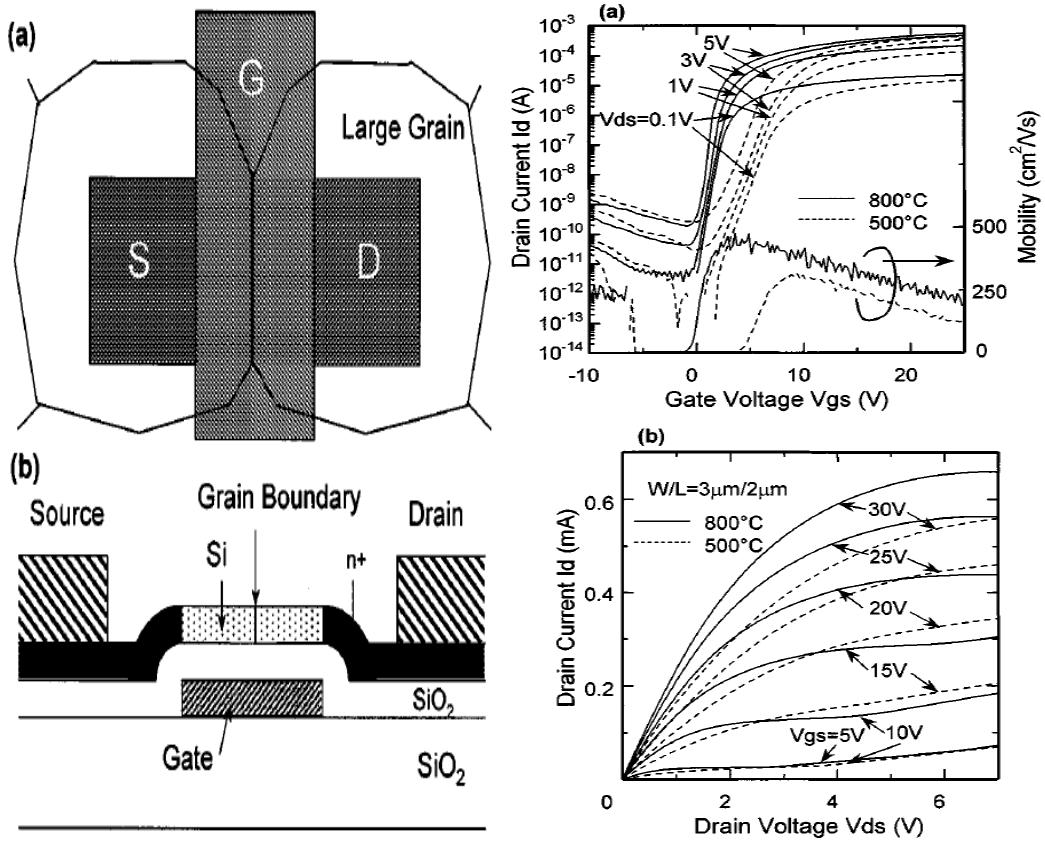

采用金属诱导横向结晶方法（Metal Induced Lateral Crystallization，MILC）可以得到具有大而规整的晶粒的 Poly-Si TFT 器件，当配合高温退火时，可以进一步得到更长更宽的晶粒，同时，缩短沟道长度和器件宽度可以减少沟道中的晶界数量，提高器件的迁移率，增强器件性能。图 3-1 显示了由高温退火 MILC 法制备的明显高于传统 TFT 性能的 A 型-经度向（平行于沟道电流传导方向）晶界和 B 型-纬度向（垂直于沟道电流传导方向）晶界器件<sup>[47]-[51]</sup>。可以明显看到，由于晶粒尺寸增加，晶界数目减少，Poly-Si TFT 器件的输出电流显著增加，器件迁移率大大增加，亚阈值特性显著变好，在器件尺寸进一步减小的情况下，可以逐渐接近单晶硅 SOI 器件的性能。实际上，在极端情况下，已经出现了沟道内只有一个

晶界的 Poly-Si TFT 器件。采用相调制准分子激光退火方法 (Phase-Modulated Excimer Laser Annealing, PMELA) 可以制造出大晶粒并且晶界位置可控的 Poly-Si TFT 器件，只有一个晶界的器件已被制造出来<sup>[40]</sup>：如图 3-2 左所示，因为源端和漏端各自处在一个完整的晶粒中，器件具有较小的泄漏电流，且因为只有一个晶界，载流子迁移率较大；如图 3-2 右所示，当工艺温度为 500 度时，器件电流开关比约为  $10^6$ ，场效应迁移率约为  $330\text{cm}^2/\text{Vs}$ ，亚阈值摆幅约为  $1.1\text{V}/\text{dec}$ ，可见单晶界器件提高了器件性能。此外，采用准分子激光退火方法 (Excimer Laser Annealing, ELA) 也制造出了单晶界器件<sup>[41]</sup>。

对于现代短沟道、大晶粒、少晶界的 Poly-Si TFT 器件来说，离散晶界效应越来越重要，它影响着器件的性能，并造成了器件的不均匀性。对于这种情况，我们需要采用分离晶界 (Discrete Grain Boundary, DGB) 方法进行研究，即认为陷阱只分布在晶界上。

图 3-1 由高温退火 MILC 法制备的明显高于传统 TFT 性能的 A 型-经度向晶界和 B 型-纬度向晶界器件<sup>[47]</sup>

图 3-2 单晶界 Poly-Si TFT 器件结构及其器件性能<sup>[40]</sup>

### 晶界数量、位置、角度及其上陷阱的影响

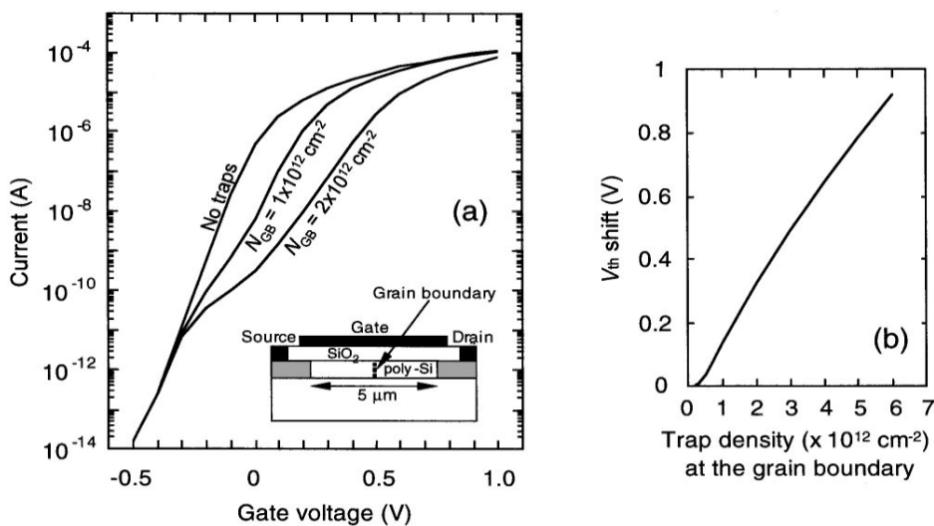

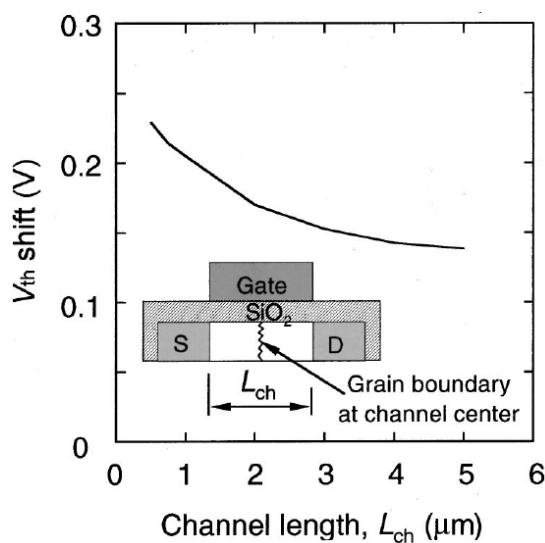

采用分离晶界方法，国际上很多研究小组对晶界的数量、位置和角度等离散晶界的几何性质给器件性能带来的影响进行了研究。Yamaguchi 利用二维数值仿真方法对具有分离晶界的 Poly-Si TFT 器件进行了仿真<sup>[54]</sup>。首先，如图 3-3 所示，当增加晶界上的陷阱浓度时，输入输出特性曲线会向右偏移，这意味着阈值电压会随陷阱浓度而改变，阈值电压的偏移定义为具有一定晶界上陷阱浓度的器件和无晶界器件的阈值电压的差别。实际上，晶界上的陷阱会陷落被吸引到表面的电子，阈值电压的增加与陷阱浓度的增加基本呈线性关系。进一步的，如图 3-4 所示，当沟道长度减小时，由陷阱所带来的阈值电压偏移会有增大的趋势，这意味着当器件尺寸变小时，由晶界所带来的器件不均匀性会增大，增强器件的均匀性是一个重要的问题。Yamaguchi 还对 Poly-Si TFT 器件中晶界的位置和数量对器件性能的影响做了仿真研究，他指出，增加晶界的数目并不会显著的增加阈值电压的偏移，这是因为阈值电压的偏移量主要由晶界上最大的陷阱浓度所决定，各晶

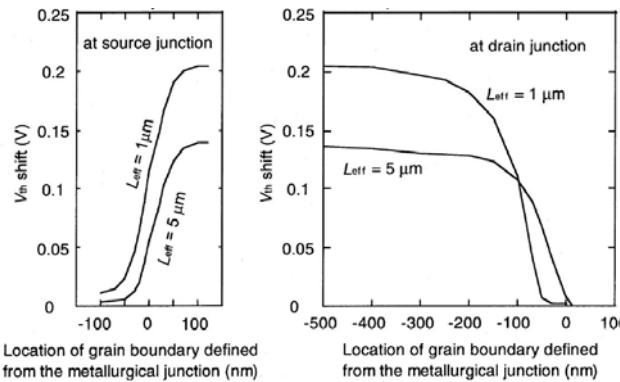

界上的陷阱浓度一致，阈值电压偏移不会有明显改变，关于这一结论还需要继续进行研究。关于晶界的位置所带给器件的影响，Yamaguchi 指出，在器件中的大部分区域内，晶界位置的改变并不会引起阈值电压偏移的改变，这同样是因为阈值电压的偏移量主要由晶界上的陷阱浓度所决定，但当晶界位置在源端或者漏端 PN 结附近时，由于晶界上陷阱不再决定阈值电压的偏移，阈值电压的偏移将会随着晶界位置的改变而改变，如图 3-5 所示。在实际器件中，晶界的位置很难控制，则器件的均匀性因此受到很大挑战，晶界的位置对器件性能的影响还有待进一步研究。

图 3-3 晶界上陷阱大小对器件性能的影响<sup>[54]</sup>

图 3-4 当器件尺寸减小时由晶界所带来的器件不均匀性会增加<sup>[54]</sup>

图 3-5 晶界位置对器件性能的影响<sup>[54]</sup>

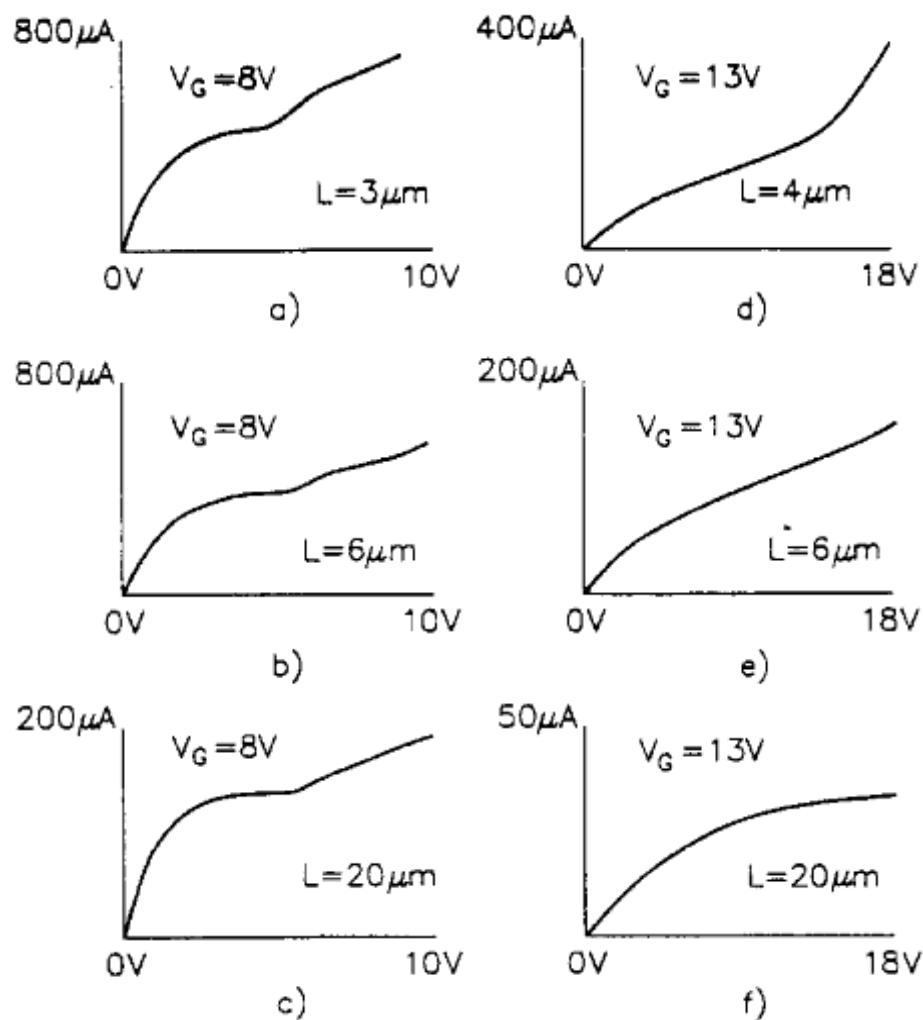

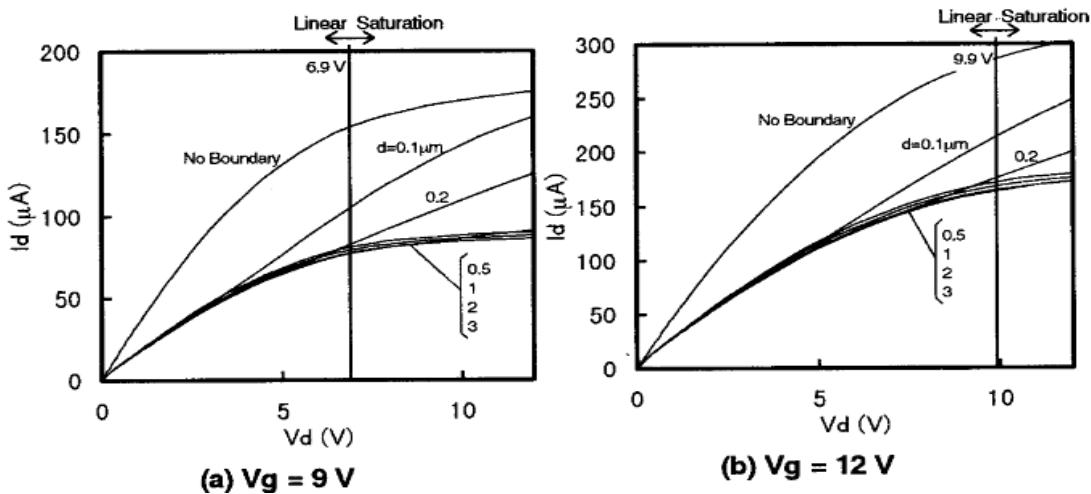

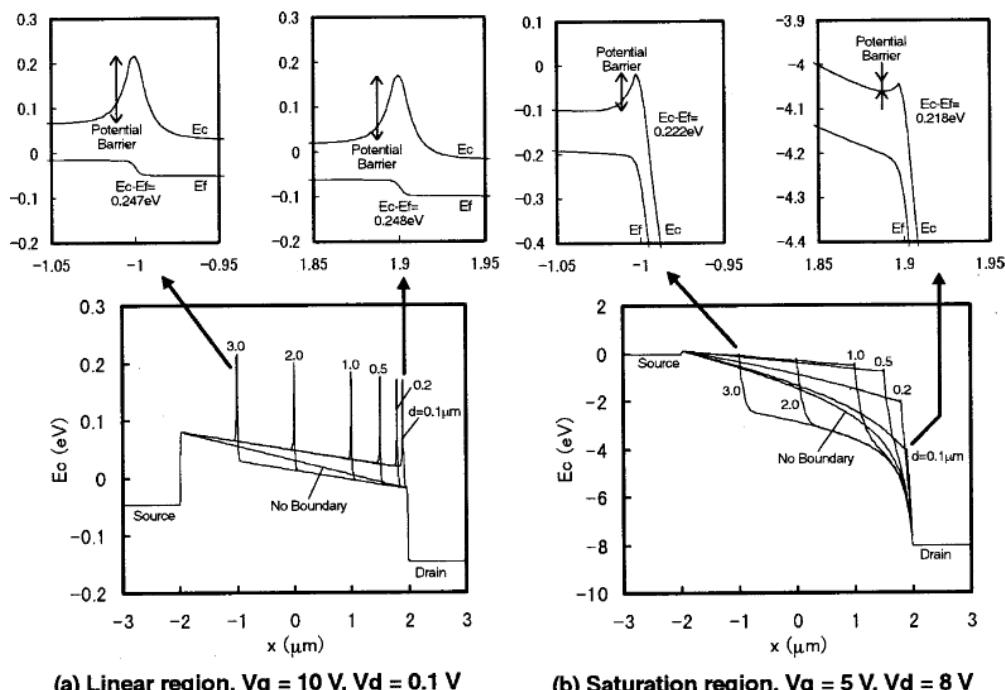

关于晶界位置对于 Poly-Si TFT 器件影响的进一步研究, Kimura 等人对此有过基于数值仿真和实验的探讨<sup>[52][53]</sup>。他们通过二维数值仿真指出, 晶界位置对器件性能的影响是通过对晶界处的势垒高度的影响来实现的, 若势垒高度减小, 则输出电流会增大。用做仿真的 TFT 器件其沟道长度为  $4\mu m$ , 具有一个晶界, 距漏端分别为  $0.1, 0.2, 0.5, 1, 2, 3\mu m$ , 其上有指数分布的陷阱能级, 即位于能带上方的一个指数分布受主陷阱以及位于能带下方的一个指数分布施主陷阱, 仿真中将让器件工作在线性区和饱和区。如图 3-6 所示, 当器件处于线性区时, 晶界位置几乎不对器件性能造成影响, 而当器件工作在饱和区时, 晶界靠近漏端的器件其电流较大, 而晶界远离漏端的器件电流大小相似。这可以通过图 3-7 所示的晶界位置对器件晶界处势垒高度的影响来解释, 即当器件工作在线性区时, 沟道内各处的势垒高度基本相同, 故晶界的位置不影响漏端电流的大小; 而当器件工作在饱和区时, 由于靠近漏端的地方被夹断, 形成高阻区, 其内有强电场, 当晶界靠近漏端, 处在夹断区中时, 其面向源端的势垒高度会被降低, 从而导致晶界靠近漏端的器件输出电流比晶界在其他地方的器件要高, 而在远离漏端夹断区的地方, 势垒高度大小基本一致, 故输出电流大小基本相同。这些结论意味着是在夹断区产生的强电场, 使得处在其中的晶界势垒发生改变, 从而改变了器件的电流特性。进一步的, Kimura 等人通过设计的实验证实了这一论断。Kimura 等人的结论非常有意义, 在实际 Poly-Si TFT 器件生产中, 由于晶界位置难以控制, 故当晶粒尺寸变大, 晶界数目变小时, 器件的性能可能会强烈的受到晶界位置的影响, 从而导致器件的均匀性变差, 这会对显示电路的性能造成很大影响。在本章下一节中, 本论文将结合 KINK 效应对晶界位置给器件性能的影响做详细分析。

图 3-6 晶界位置对器件输出特性曲线的影响<sup>[53]</sup>图 3-7 晶界位置对器件晶界处势垒高度的影响<sup>[53]</sup>

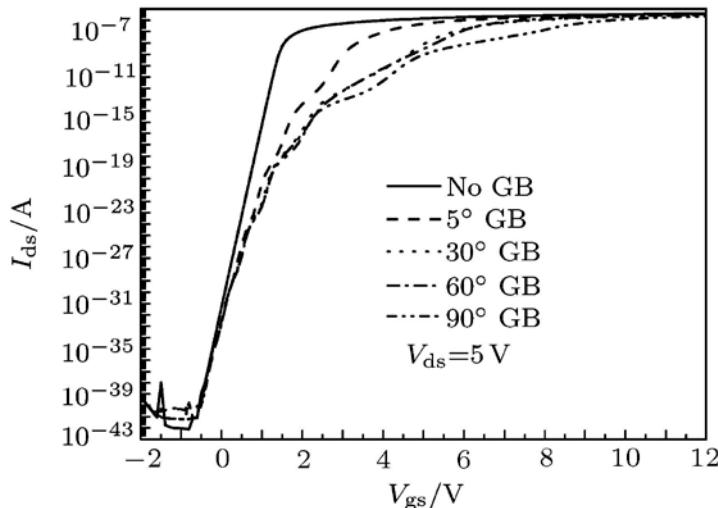

此外, 如图 3-8 所示, Zhou 等人对晶界角度给器件带来的影响进行了分析, 他们指出, 当晶界角度由 0 度变为 90 度时, 器件的输出电流将由大变小, 这也可以通过晶界角度给晶界处势垒高度带来的影响来分析, 即当晶界角度为 90 度时, 其晶界处势垒高度最大, 器件电流受到最大的影响; 而当晶界角度变为 0 度时, 势垒消失, 带给器件电流的影响消失。这里需要指出的是, 尽管与电流方

向平行的晶界会给器件的输出电流带来更小的衰减，器件的性能更理想，但同时也给器件带来了潜在的泄露通道，即源漏之间的晶界可能会在器件尺寸很小时带来器件的源漏穿通和较大的泄漏电流，这对于有较大栅宽的器件尤为明显，因为栅宽较大的器件可能有更多的与电流方向平行的晶界。

图 3-8 晶界角度对器件转移特性曲线的影响<sup>[55]</sup>

### 多晶材料和器件中晶界处的碰撞电离现象

Poly-Si TFT 器件中的多晶硅薄膜作为多晶材料的一种，可能会在晶界处发生碰撞电离现象。实际上，对于多晶材料，已有实验证明，对于多晶 GaAs 和 ZnO，其晶界处可能发生碰撞电离现象，碰撞电离产生的载流子将会影响晶界处的势垒分布，从而影响电流的传导机制<sup>[56][57]</sup>。而对于 Poly-Si，已有工作报道了在 Poly-Si 电阻薄膜和 Poly-Si PN 结中与晶界处的碰撞电离相关的现象<sup>[58][59]</sup>。

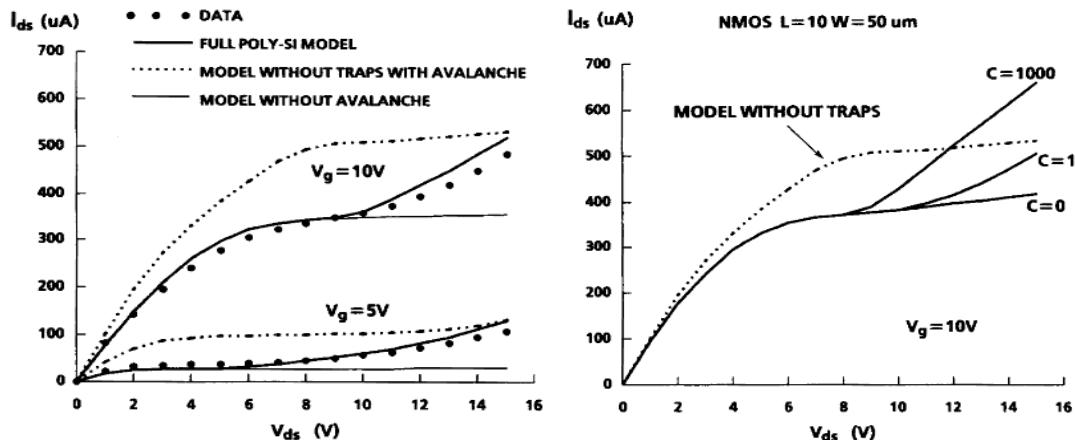

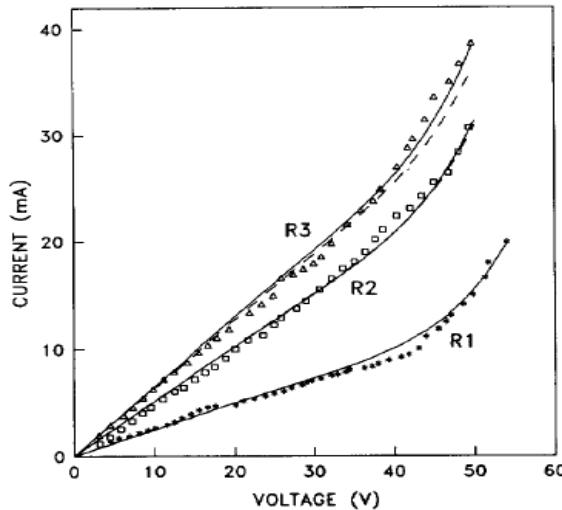

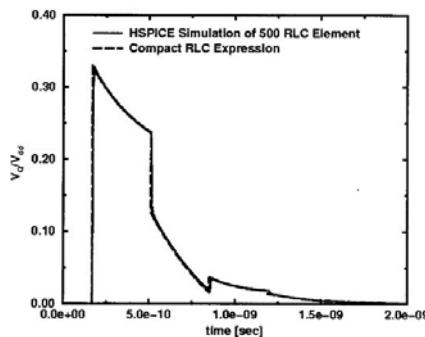

在器件的实际工作状态中，高电压高电场的情况十分普遍而重要。如图 3-9 所示，当 Poly-Si 薄膜电阻两端加上大的偏置电压时，会发生电流突增现象。Das 等人认为这正是由 Poly-Si 薄膜中晶界附近的碰撞电离效应所带来的<sup>[58]</sup>。他们对 Poly-Si 薄膜电阻进行了基于物理的建模，在晶界处电子发射理论的基础上，考虑了晶界处的碰撞电离。对于中等或重掺杂的 Poly-Si 薄膜电阻，因为晶粒相对于晶界具有低得多的电阻，故外加偏置电压将会主要降落在晶界上，因为晶界非常薄，故晶界中的电场强度将会非常大。当外加偏置电压足够大时，晶界中的电场将会足够大而引起碰撞电离现象。Das 等人用倍增因子  $M_n$  来描述晶界处的碰撞

电离效应给原电流  $I$  带来的影响，总电流  $I_{\text{tot}}=M_n I$  将会因此发生突增，如图 3-9 所示，理论模型和实验数据拟合的很好，其中电阻 R1, R2, R3 具有不同的宽度。需要指出的是，晶界处的碰撞电离现象是一个级联过程，而 Das 的模型只用一个因子综合描述了这一现象，在本章第 3 节会对此深入讨论。

图 3-9 在多晶硅薄膜电阻中由晶界处的碰撞电离造成的电流突增现象<sup>[58]</sup>

对于 Poly-Si PN 结，同样有关于晶界附近碰撞电离现象的报道。如图 3-10 所示，对于 Poly-Si PN 结，当外加的反向电压足够大时，会发生击穿现象。在单晶硅 PN 结中，这种击穿现象主要是因为在 PN 结空间电荷区中发生的碰撞电离现象，但 Amrani 等人发现，对于 Poly-Si PN 结，其击穿电压要比单晶硅 PN 结小得多<sup>[59]</sup>。为解释并研究这一现象，他们进行了二维数值仿真研究，将晶界近似的认为呈垂直或平行于电流的传导方向分布。他们发现，正是晶界上的陷阱分布导致了 Poly-Si PN 结击穿电压相对于 Si PN 结的降低。晶界上存在的陷阱耗尽了其附近的区域，形成了空间电荷区，在外加较大的反向电压时，相比于单晶硅 PN 结，Poly-Si PN 结不仅具有冶金结附近的空间电荷区可以发生碰撞电离，还具有晶界附近的诸多空间电荷区可以发生碰撞电离现象，这相当于总的碰撞电离区域长度的增加，所以，Poly-Si PN 结的击穿电压被大大降低了，对于 Poly-Si PN 结内部电场和电势分布的分析进一步证实了这一点，即晶界附近具有远大于晶粒内部的电场强度，可以发生碰撞电离。进一步的研究表明，击穿电压将随着晶界处陷阱浓度的增加而下降。

图 3-10 在多晶硅 PN 结中与晶界处的碰撞电离相关的击穿现象<sup>[59]</sup>

### 晶界处的势垒高度建模问题

如前所述,由于晶界的离散性质,离散晶界效应给 Poly-Si TFT 器件带来了独特的影响,但无论是晶界位置、数目和其上陷阱的影响,晶界处电场强度和碰撞电离现象,还是其他相关电流传导机制问题,都可以转化为晶界处电势分布和势垒高度的相关问题,即 Poly-Si TFT 的离散晶界效应的核心是晶界处的电势分布和势垒高度问题。为进一步研究离散晶界效应,量化晶界处的电势分布和势垒高度,从而量化 Poly-Si TFT 的输出电流特性,并对 Poly-Si TFT 建立精简模型,一直以来都是 Poly-Si TFT 研究的核心问题。

对于晶界处势垒模型的建立,必须注意到,当漏端电场较大时,在沟道表面,晶界处的势垒分布会受到该电场的影响而改变分布,由对称分布变为不对称,靠近源端的势垒高度被降低,靠近漏端的势垒高度增加,这将导致有更多的电子可以从降低了的势垒一侧注入,从而导致电流的增大,此即 DIGBL 效应。DIGBL 效应在大漏端电压的情形下非常重要,晶界处势垒模型必须能够反映 DIGBL 效应。同时,如前所述,晶界位置的改变将会影响 DIGBL 效应,即当漏端电场较大时,晶界越靠近漏端,则 DIGBL 效应越严重,晶界处势垒模型也需要考虑到晶界位置对 DIGBL 效应的影响。国际上很多研究小组对晶界势垒模型和 DIGBL 效应做出了

贡献。

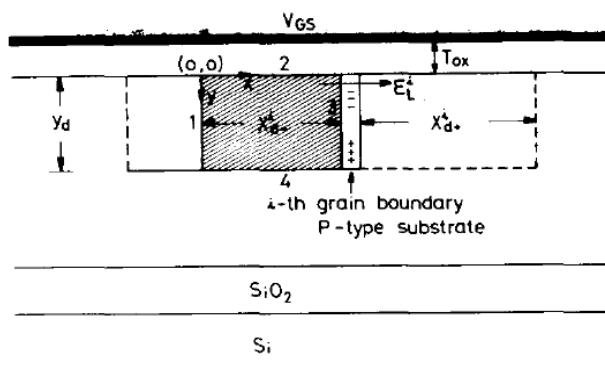

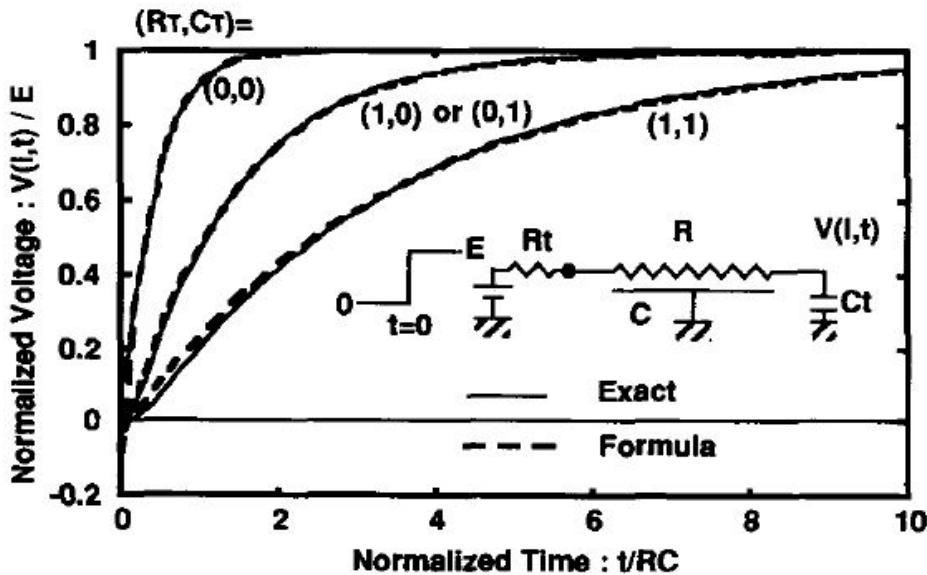

Lin 等通过求解准二维泊松方程，得到了考虑离散晶界的 Poly-Si TFT 表面势分布模型<sup>[60]</sup>，并将漏端电压在沟道中产生的影响即 DIGBL 效应考虑了进去。如图 3-11 所示，对于由边界 1,2,3,4 所围成的区域，Lin 等通过近似，将描述其电势分布的二维泊松方程转化成了一维问题，即求解如下方程：

$$\frac{\partial^2}{\partial x^2} \phi(x) - K^2 \phi(x) = -K^2 V_{QN}^i \quad (3-1)$$

其中， $\Phi(x)$  是表面沟道  $(x, 0)$  处的电势与原点处的电势的差值， $K$  是常数， $V_{QN}^i$  含有栅极电压和原点处的电势。应用适当的边界条件，其解为：

$$\phi(x) = V_{QN}^i - V_{QN}^i \cosh(Kx) \quad (3-2)$$

则由此可把晶界处的电势与沟道中的源漏电场  $E_L^i$  联系起来：

$$KV_{QN}^i \sinh(Kx_{d\mp}^i) = \frac{Q_{GB\mp}^i}{2\epsilon_{si}} \mp E_L^i \quad (3-3)$$

其中的晶界上的陷阱电荷  $Q_{GB}^i$  在器件工作在开态时被认为是始终填满的。由此可最终得到考虑了 DIGBL 效应的晶界处势垒高度模型：

$$\Psi_{B\mp}^i = \frac{y_{dinv}}{3} \frac{1}{C_{ox}(V_{GS} - V_{To} - V_i)} \cdot \frac{(qN_{st} \mp \epsilon_{si}E_L^i)}{8\epsilon_{si}} \quad (3-4)$$

可以看到，晶界左侧 (-) 与右侧 (+) 的势垒高度是不同的，且受电场  $E_L^i$  影响，左侧的势垒高度较小，即呈现了 DIGBL 效应。尽管如此，Lin 等并没有考虑到晶界位置对 DIGBL 效应的影响，在具体应用其势垒模型到电流的计算中时，为简化，他们近似的认为在不同的位置上的晶界受到的电场的影响是相同的。

图 3-11 Lin 用于求解 Poly-Si TFT 表面势分布的示意图<sup>[60]</sup>

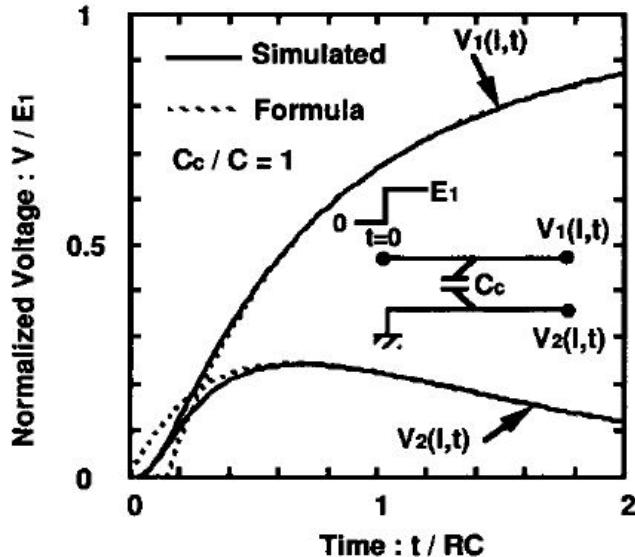

此外, Chen 等对于本征材料的 Poly-Si TFT 器件进行了研究<sup>[61][62]</sup>, 他们利用电中性近似和高斯定理分别对栅电压在阈值电压以下和以上的情况进行了分析, 得到了晶界处的势垒高度模型, 类似的, 他们也考虑了与晶界位置无关的 DIGBL 效应。Wu 等通过求解准二维泊松方程<sup>[63]</sup>, 并利用高斯定理和电荷守恒定律解释了在发生 DIGBL 效应时, 晶界两侧势垒高度的下降量和上升量并不相等, 而是势垒高度的下降量要小于势垒高度的上升量, 同样他们也没有考虑晶界位置的影响。Ho 等利用电位叠加原理和镜像电荷方法<sup>[64]</sup>, 得到了能考虑 Poly-Si TFT 中晶界三维分布的表面势模型, 该模型能够考虑晶界位置的影响, 在本章第四节中, 本论文将采用求解准二维泊松方程并利用高斯定理的方法<sup>[65]</sup>, 给出准确而更简洁的能考虑晶界位置对 DIGBL 效应影响的势垒高度模型。在得到势垒高度模型以后, 可以基于晶界处的热电子发射机制、漂移扩散机制或者同时包括两者在内的复合机制对 Poly-Si TFT 的电流传导进行建模<sup>[66]-[75]</sup>, 并可进一步考虑 KINK 效应等影响。可见, 晶界处的势垒高度建模问题是 Poly-Si TFT 电流建模的核心问题, 是晶界问题的核心问题, 因而十分关键。

除上面简述的晶界问题之外, 关于离散晶界效应还有许多的问题有待解决。A. Valletta 分析了晶粒内陷阱, 晶界处电流传导和晶界厚度对器件性能的影响<sup>[44]</sup>; V.W. Chan, M. Chan 等人分析了经度方向和纬度方向的晶界性质的异同<sup>[46]-[50]</sup>; M. Chan 等人分析了晶界分布的不确定性给器件带来的均匀性的影响<sup>[51]</sup>; 此外, M.Wong, W. Eccleston, F. Farmakis, K. sharma 等人均对晶界做了广泛而有意义的分析<sup>[66]-[75]</sup>。本论文所研究的离散晶界效应将主要集中在如前所述的晶界的陷阱、数目和位置对器件的影响, 晶界处的碰撞电离现象, 以及晶界处势垒高度模型等方面, 以下各节将采用数值仿真和解析建模方法进行讨论。

## 3.2 晶界的数目、位置及其上陷阱浓度对 KINK 效应的影响

晶界上的陷阱浓度、晶界的数目和晶界的位置会对 Poly-Si TFT 器件的性能带来影响, 尤其是当晶粒尺寸变大、器件沟道长度变短时, 这种影响会变大, 这种影响会给器件的均匀性带来问题, 从而影响面板的性能。与此同时, 由于 Poly-Si TFT 的悬浮衬底结构, 它还会有严重的 KINK 效应, 这使得离散晶界效应会和 KINK 效应相互影响。通过上一章对 KINK 效应的分析, 我们知道, KINK 效应的关键是

漏端高场区所发生的碰撞电离效应和由碰撞电离空穴开启源体 PN 结所带来的寄生晶体管效应，离散晶界效应对 KINK 效应的影响将主要通过对寄生晶体管和碰撞电离的影响来进行，本节将利用二维数值仿真对 Poly-Si TFT 器件中晶界所带来的影响进行分析，讨论晶界的数目、位置和其上陷阱浓度对 KINK 效应的影响。

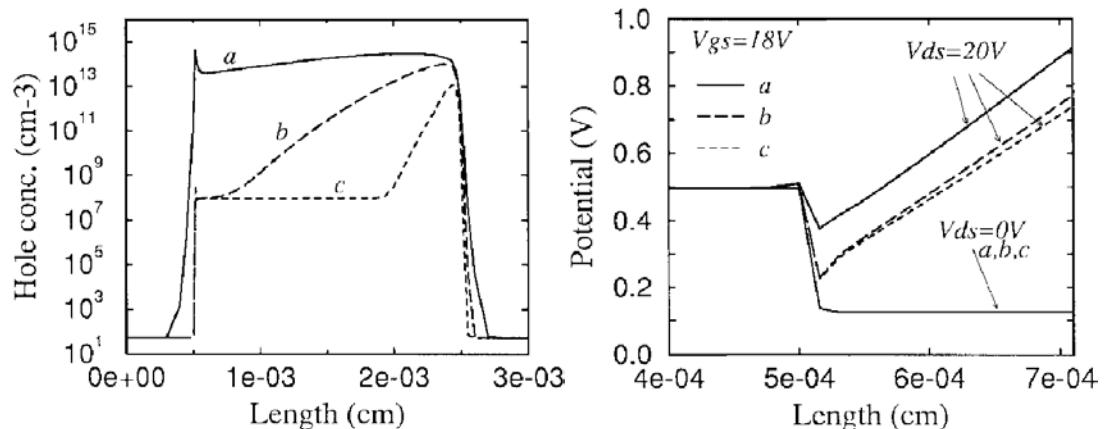

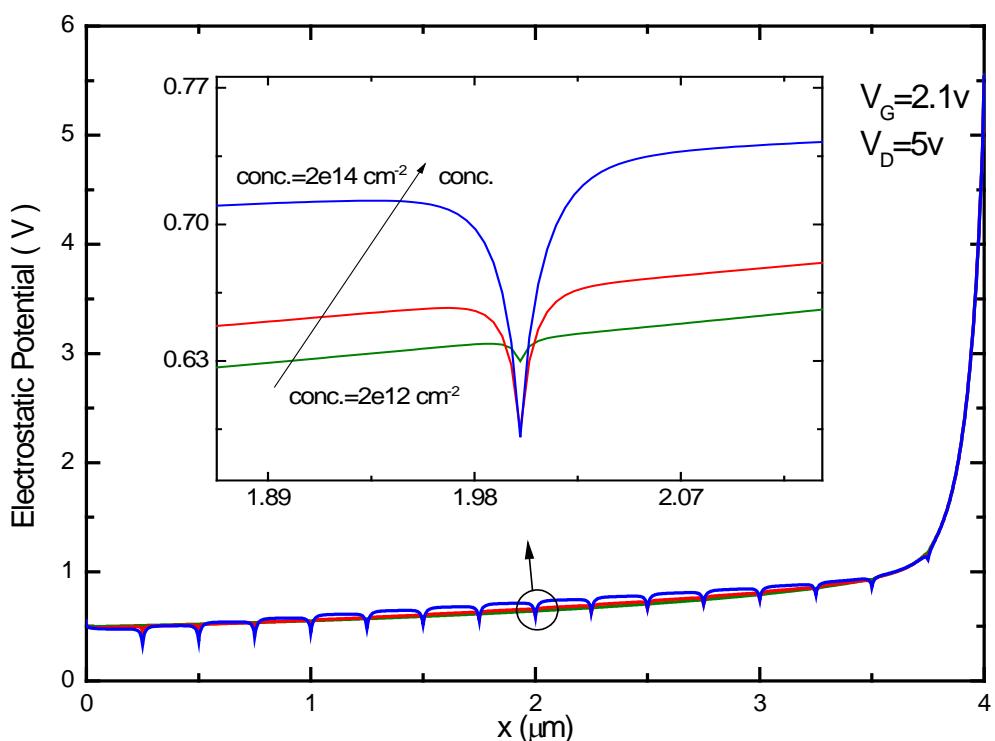

二维数值仿真通过 Sentaurus Device TCAD 工具来进行。Poly-Si TFT 器件的沟道长度为  $4\mu\text{m}$ ，栅氧层厚度为  $40\text{nm}$ ，硅膜厚度为  $40\text{nm}$ ，薄膜掺杂浓度为  $1.5 \times 10^{17}\text{cm}^{-3}$ 。为分析晶界的离散性质对器件性能的影响，仿真采用了分离晶界方法，认为陷阱只分布在分离的晶界上，晶粒宽度为  $250\text{nm}$ ，晶界上分布有单能级的施主和受主陷阱，分别与价带和导带相距  $0.15\text{eV}$ ，栅极偏置电压为  $2.1\text{V}$ 。仿真采用了不同陷阱浓度、晶界数目和晶界位置。

### 3.2.1 晶界上陷阱浓度对 KINK 效应的影响

如图 3-12 所示，当器件中晶界上的施主和受主陷阱浓度由大到小变化时，寄生晶体管集电极电流将增大，其电流增益也将随之增大。之前，有文献报道，当陷阱俘获横截面的过分增加时，过于强烈的复合效应会导致寄生晶体管的无法开启，但当寄生晶体管开启时，如上一章所述，复合效应与产生效应相比很微弱，可以忽略不计，故导致寄生晶体管集电极电流随陷阱浓度的减小而增大的主要原因将不是复合效应的显著减弱。实际上，如图 3-13 所示，在沟道表面，当晶界上的陷阱浓度减小时，其势垒高度会随之减小，这是因为当陷阱浓度减小时会有更少的电子电荷落到晶界上的陷阱中，从而导致晶界附近更窄的空间电荷区，更小的电场强度和更低的势垒。晶界处的电流传导机制主要是热电子发射机制，当晶界处势垒降低时，沟道内的电流将会随之增加，因为寄生晶体管中的集电极电流将会在栅电压的作用下，主要在沟道表面做漂移运输，故集电极电流也会随势垒高度的降低而增大，与此同时，寄生晶体管效应将使得集电极电流  $I_c$  与原沟道内电流  $I_0$  的比值增大，由上一章的分析可知，KINK 效应可由比值  $\Delta I/I_0 = 1 - [M(I_c/I_0 + 1)]^{-1}$  来衡量，碰撞电离因子  $M$  基本不变，则 KINK 效应将变强。此外，因为基极电流由集电极电流和沟道电流共同通过碰撞电离产生，故集电极电流与基极电流的比值即电流增益会随着晶界处陷阱浓度的减小而增加。

### 3.2.2 晶界数目对 KINK 效应的影响

如图 3-14 所示, 当 Poly-Si TFT 器件中的晶界数目开始减小, 由 15 个变为 7 个和 3 个时, 亦即晶粒尺寸开始增加时, 寄生晶体管中的集电极电流将会增加, 电流增益也会增加, 这意味大晶粒、少晶界器件将会具有更加强烈的 KINK 效应。同样, 这可以通过晶界处势垒高度的变化来解释, 如图 3-15 所示, 当晶粒尺寸增加时, 晶界处的势垒高度将会减小, 图中当晶界变为 3 个时, 晶界处的势垒高度几乎消失。这是因为当晶界数目减小时, 由于器件中的陷阱减少, 其阈值电压将会减小, 相同的栅电压将会在沟道表面吸引更多的沟道电子, 从而减小了晶界附近的空间电荷区, 降低了晶界附近的电场强度和势垒高度, 从而沟道中的传导电流会增加, 故寄生晶体管的集电极电流会随着晶界数目的减小而增大, 同上一小节的分析, KINK 效应将增强, 电流增益也将增大。现代 Poly-Si TFT 器件向着大晶粒、少晶界的方向发展, 从本小节的分析结果来看, 尽管大晶粒器件会带来更大的迁移率、更好的亚阈值特性等好的性能, 它也会同时带来更大的 KINK 效应, 需要在设计上给予考虑。

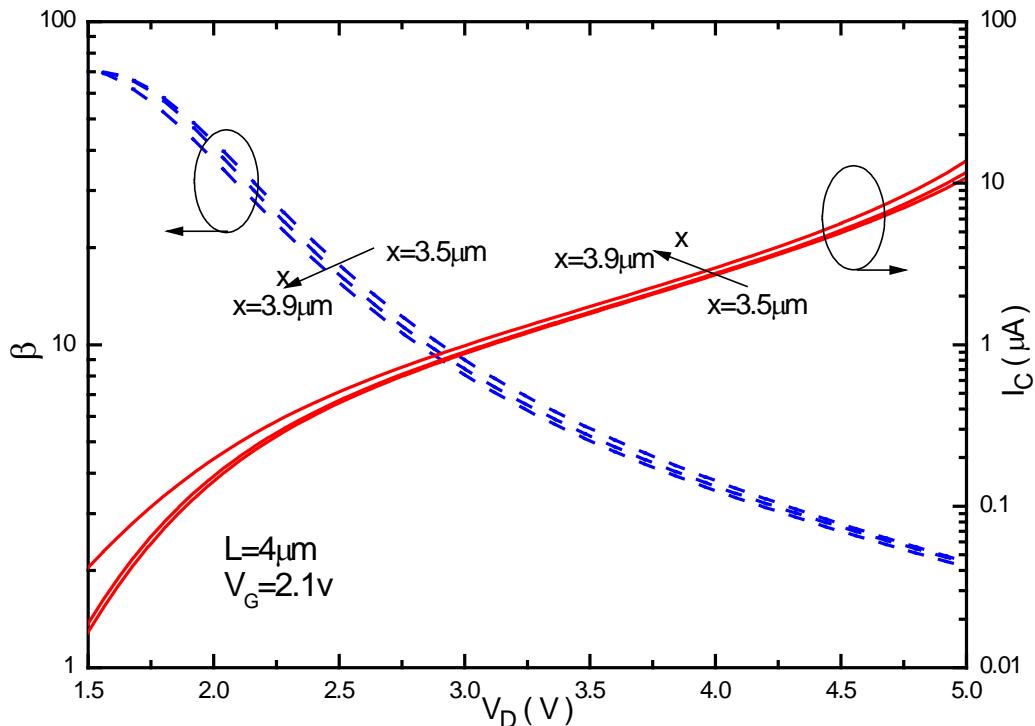

### 3.2.3 晶界位置对 KINK 效应的影响

如图 3-16 所示, 在对 Poly-Si TFT 器件的仿真中, 现在只考虑一个晶界的情况, 分别让它距离漏端  $3.5\mu\text{m}$ ,  $3.75\mu\text{m}$ ,  $3.9\mu\text{m}$ , 则当晶界接近漏端时, 寄生晶体管的集电极电流增加, 而电流增益下降。这可以由图 3-17 所示的晶界处的势垒高度随晶界位置的变化来解释。如图所示, 在靠近漏端夹断区具有很大的电阻, 漏端电压将主要降落于此, 造成很高的电场强度, 当晶界靠近漏端时, 其势垒高度会受到强电场影响, 即发生 DIGBL 效应, 面向源端一侧的势垒高度会被降低, 且越靠近漏端, DIGBL 效应越明显, 势垒被降低的越多, 从而使得沟道电流越大, 寄生晶体管集电极电流也越大, 同上分析可有  $I_c/I_0$  也越大。与上两小节情况不同的是, 晶界的右移会导致电场的增强和碰撞电离因子  $M$  的增大(在图 3-28 及 3-29 中更明显), 可见比值  $\Delta I/I_D=1-[M(I_c/I_0+1)]^{-1}$  和 KINK 效应将随晶界的右移而加强, 但碰撞电离的增强将导致基极电流与集电极电流的比值增大, 导致了增益的下降, 这和晶界上陷阱浓度和数目带来的影响不同。

图 3-12 寄生晶体管集电极电流和电流增益随晶界上陷阱浓度的变化

图 3-13 Poly-Si TFT 器件沟道表面的电势分布随晶界上陷阱浓度的变化

图 3-14 寄生晶体管集电极电流和电流增益随晶界数目的变化

图 3-15 Poly-Si TFT 器件沟道表面的电势分布随晶界数目的变化

图 3-16 寄生晶体管集电极电流和电流增益随晶界位置的变化

图 3-17 Poly-Si TFT 器件沟道表面的电势分布随晶界位置的变化

### 3.3 多晶硅薄膜晶体管中的晶界处碰撞电离现象

#### 3.3.1 输出特性曲线中的大电流现象

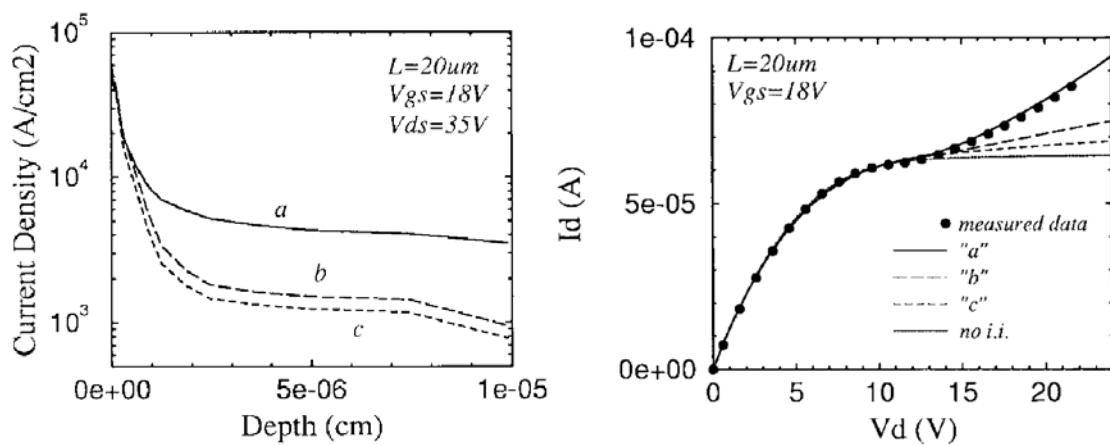

如前所述，对于多晶材料，已有晶界处的碰撞电离现象的报道。对于 Poly-Si 材料，已有 Poly-Si 薄膜电阻和 Poly-Si PN 结中晶界附近的碰撞电离现象的报道。对于 Poly-Si TFT，相对于电阻和 PN 结，它最大的特点在于有栅电压的作用，为研究 Poly-Si TFT 中晶界处的碰撞电离现象，本小节将利用 Sentaurus Device TCAD 工具对其进行二维数值仿真，通过仿真结果可以观测器件内部产生率的分布。我们将看到，由于晶界处的碰撞电离效应，Poly-Si TFT 器件的电流输出特性曲线和转移特性曲线会具有独特的性质，同时，晶界处的碰撞电离亦会引发独特的 KINK 效应。

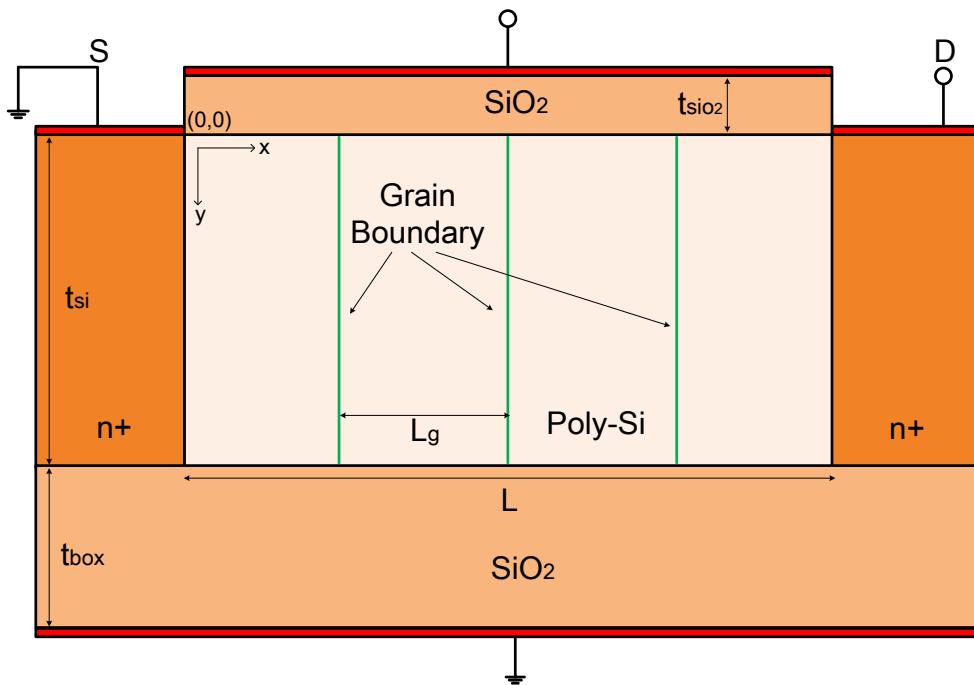

如图 3-18 所示，用于仿真的 Poly-Si TFT 器件栅氧层厚度为 50nm，硅膜厚度为 50nm，沟道长度为  $4\mu\text{m}$ 。为呈现晶界的离散性质，仿真采用分离晶界方法，认为陷阱只分布在晶界上，晶粒长度为 250nm，其上分布有施主和受主陷阱，陷阱能级为单能级，分别距价带和导带 0.15eV，陷阱浓度为  $5 \times 10^{13} \text{ cm}^{-2}$ ，电子的俘获横截面对于施主和受主能级分别是  $1 \times 10^{-17} \text{ cm}^{-2}$  和  $1 \times 10^{-15} \text{ cm}^{-2}$ ，空穴则相反。

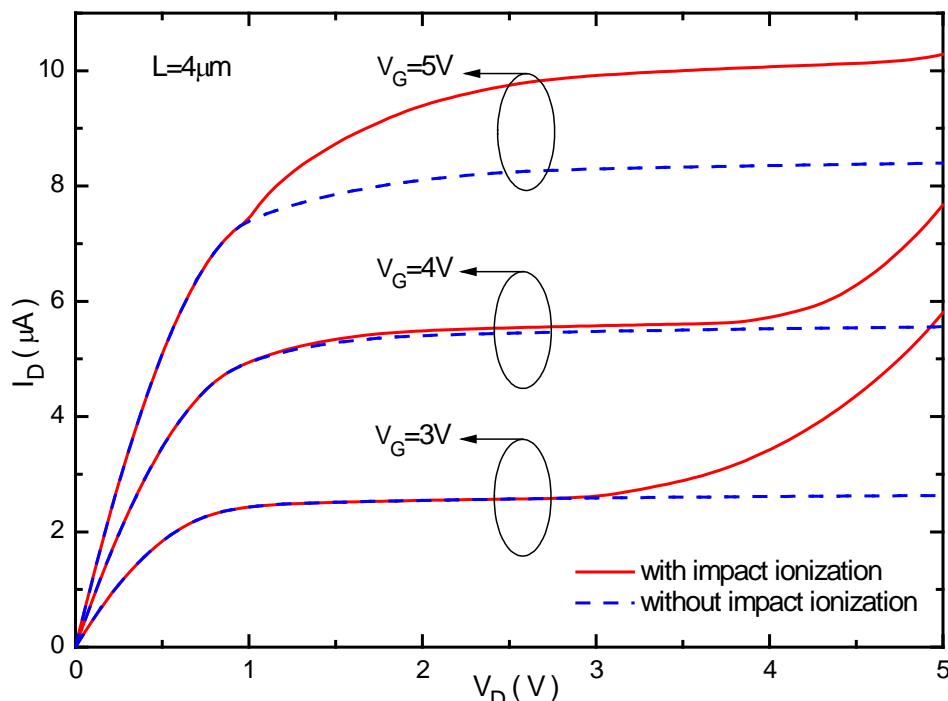

图 3-18 用于仿真的 Poly-Si TFT 结构示意图

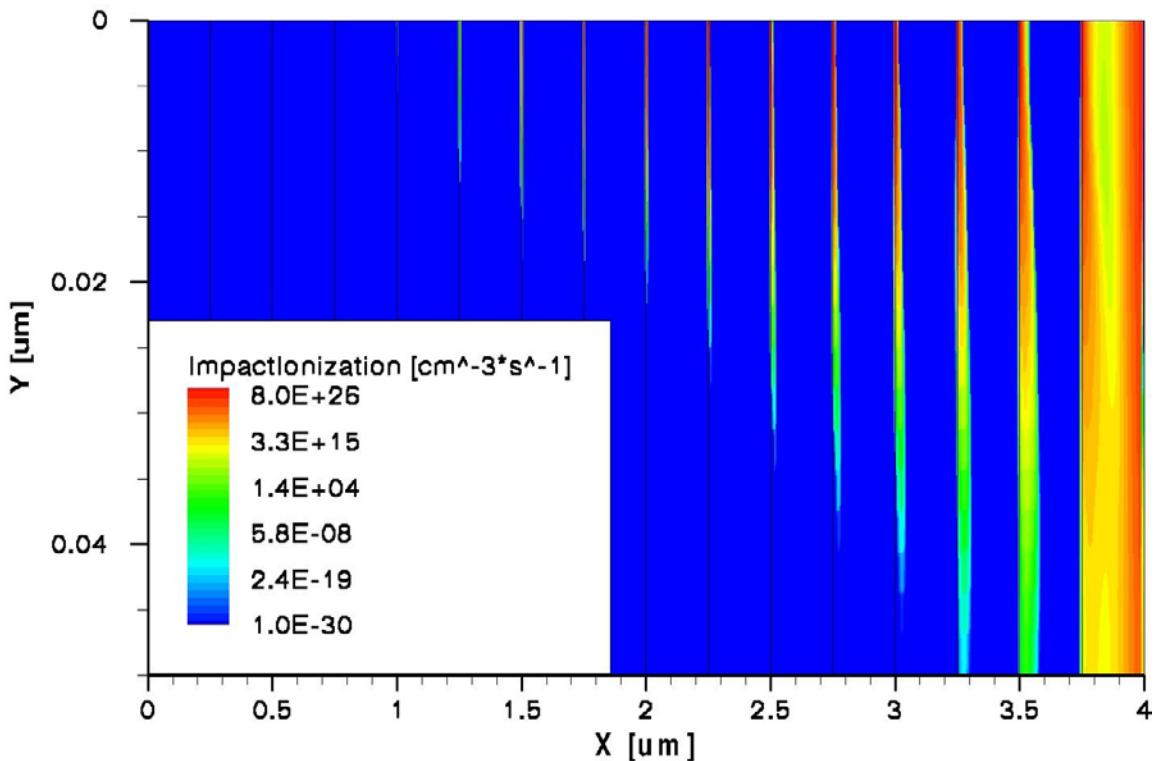

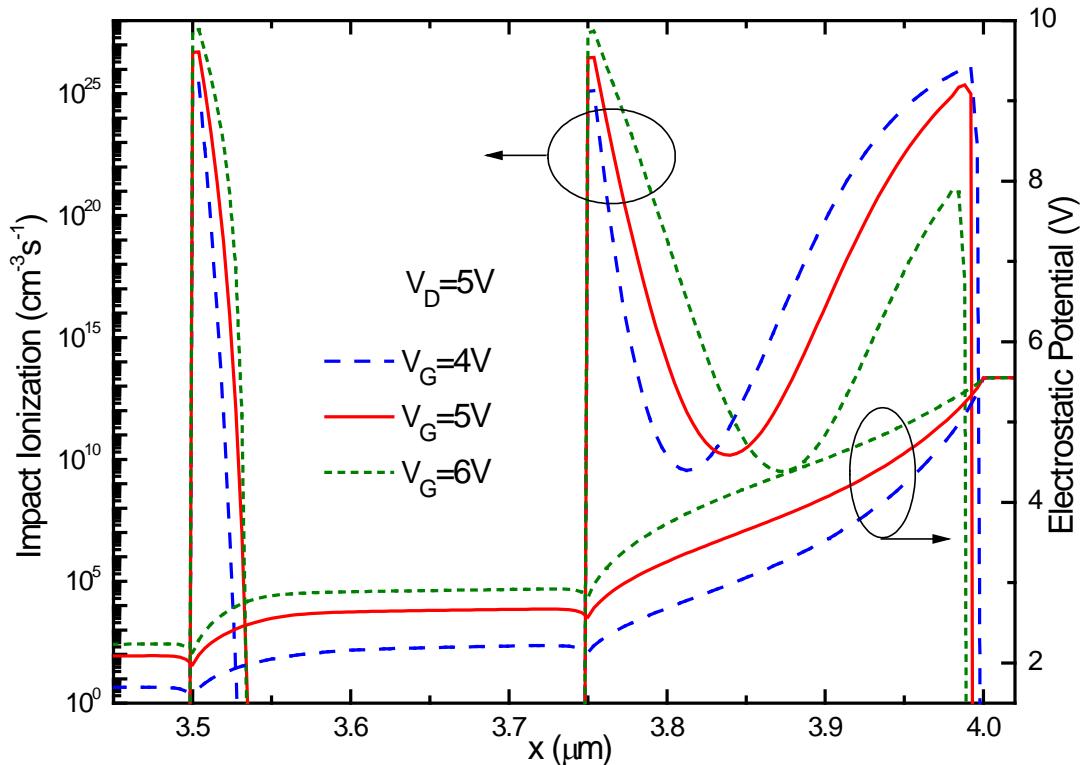

仿真结果如图 3-19 所示，在仿真过程中，栅极电压分别选取 3,4,5V，漏极电压从 0V 扫描至 5V，通过将碰撞电离模型打开和关闭分别作出了考虑碰撞电离时的输出特性曲线（红实线）和没有碰撞电离现象发生时的曲线（蓝虚线）。从图中可以明显的看到，当栅极电压较小时，考虑与不考虑碰撞电离所得到的仿真结果的差别只在于高漏端电压时的电流突增效应，即 KINK 效应，即当漏端电压较高时，其靠近漏端处被夹断，电阻很高，漏端的电压将主要降落于此处，造成碰撞电离，由碰撞电离产生的空穴在体区堆积，打开了源体 PN 结，使得电子大量注入并再次在漏端形成碰撞电离，从而造成电流突增，这在上一章已经详细分析。然而随着栅极电压的增加，可以看到，在漏端电压达到可以发生一般的 KINK 效应之前，考虑了碰撞电离效应的输出电流就要开始高于未考虑碰撞电离的情形，当栅极电压达到 5V 时，这一情形已经非常明显，这意味着除了漏端以外，还有其他地方发生了碰撞电离效应，使得输出电流增大了。为此，我们在图 3-20 中示出了碰撞电离产生率在 Poly-Si 体内的分布图，漏端电压为 2V，栅极电压为 5V。从图中可以明显的看到，除了在漏端出现了碰撞电离现象以外，在晶界附近 - 确切的说是在晶界面向漏端的那一侧，也发生了碰撞电离效应，越靠近漏端的晶界附近其现象越明显。这一晶界处的碰撞电离现象显然与输出电流的增大有关，下面进行具体分析。

图 3-19 输出特性曲线中电流的增大现象

图 3-20 晶界附近的碰撞电离现象

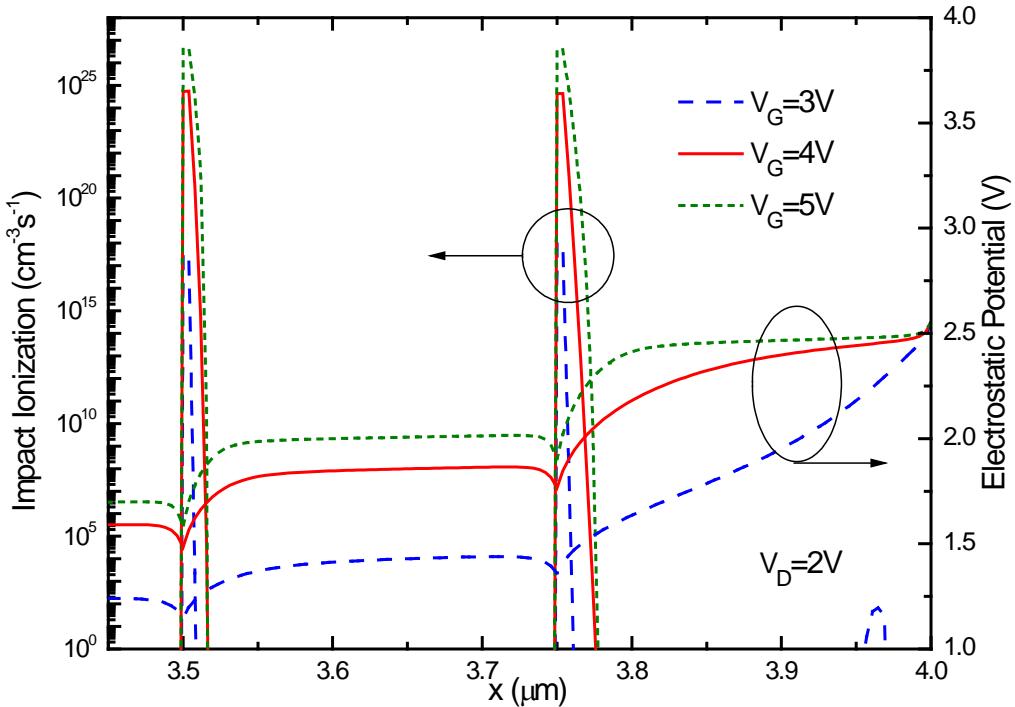

图 3-21 晶界附近的电势分布和产生率分布曲线（漏端电压为 2V）

我们在图 3-21 中, 画出了最靠近漏端的两个晶界及其附近的沟道表面在漏端电压为 2V 时的电势分布曲线以及碰撞电离产生率分布曲线。如图所示, 当栅极电压为 3V 时, 漏端的电压将主要降落在最靠近漏端的晶界与漏端之间的区域上, 即漏端具有较高电阻的区域, 然而此时的电场强度不够大, 不足以在漏端引发明显的碰撞电离效应, 同时晶界附近的碰撞电离效应同样十分微弱, 故在图 3-19 中, 当漏端电压为 2V, 栅极电压为 3V 时, 考虑碰撞电离效应的输出曲线与未考虑的曲线基本重合; 当栅极电压为 4V 时, 因为漏端附近沟道内电子的增多, 其电阻将有所减少, 与此同时, 晶界附近的电子将陷落在晶界上的陷阱中, 所形成的空间电荷区将继续具有较高的电阻, 考虑到 DIGBL 效应, 即晶界附近电场会使得晶界两边靠近漏端一侧的电场增强, 空间电荷区增大, 而另一层的空间电荷区减小, 可以知道原先主要降落在漏端的电压将开始主要转移到晶界靠向漏端一侧的空间电荷区上, 这样, 晶界靠向漏端一侧的碰撞电离产生率将开始增加, 这导致了输出电流的增加, 如图 3-19 中当漏端电压为 2V, 栅极电压为 4V 的情况; 当栅极电压为 5V 时, 漏端附近电子进一步增多, 漏端电压降落在其上的电压降进一步减少, 被进一步被转移到晶界靠近漏端一侧的空间电荷区上, 使得此处的碰撞电离产生率进一步增强, 出现了如图 3-19 所示的, 在漏电压为 2V 时所发生的相较于未考虑碰撞电离效应时的大电流现象。

### 3.3.2 转移特性曲线中的翘曲现象

在发生晶界处的碰撞电离效应时, 除了输出特性曲线中的大电流现象, 还可以在转移特性曲线中观察到电流翘曲现象。如图 3-22 所示, 在转移特性曲线中, 当栅极电压较大时, 电流会发生翘曲现象, 这种现象在漏端电压较大时更加明显。我们在图 3-23 中画出了当漏端电压为 5V 时, 在栅压分别为 4,5,6V 时, 沟道表面的电势分布曲线和碰撞电离产生率分布曲线(注意图 3-21 和图 3-23 静电势纵坐标轴显示范围分别是 1-4V 和大约 2-10V)。如图 3-23 所示, 当栅极电压为 4V 时, 5V 的漏端电压将在漏端产生沟道的夹断, 形成高阻区, 漏端电压将主要降落在夹断区, 形成强电场, 从而碰撞电离产生率很大, 将引发 KINK 效应和大输出电流; 当栅极电压增加到 5V 时, 由于漏端附近电子数目的增加, 会使得其电阻降低, 其上的电压降将降低, 电场强度下降, 碰撞电离率减小, KINK 效应变弱,

输出电流将减小；而当栅压进一步增加到 6V 时，漏端的电压降将进一步减小，如前所述，由于晶界陷落了电子并形成空间电荷区，结合 DIGBL 效应，这部分降低的电压降将被主要转移到晶界靠近漏端一侧的空间电荷区上，使得该区电场强度增加，碰撞电离产生率增加，输出电流将增大。这就解释了漏端电压较大时转移特性曲线较明显的翘曲现象。

通过对 Poly-Si TFT 器件输出特性曲线和转移特性曲线的上述分析我们可以知道，在晶界处，原本加在漏端附近的电压降会在一定条件下被转移到到晶界附近靠近漏端一侧的空间电荷区上，该区的电场强度将增加，碰撞电离率将随之增大，从而输出电流会受到影响。这一转移正是通过栅压的作用来实现的，即当栅压增大时，会增大漏端附近的电子浓度，从而减小其电阻值和分压能力，这正是 Poly-Si TFT 相比于 Poly-Si 薄膜电阻和 PN 结的特别之处。这一仿真结论有助于分析和理解有关 Poly-Si TFT 晶界处的碰撞电离现象，同时也存在潜在的应用价值，但进一步研究需要通过实验来验证和指导。在实验中，如何得到大而规整的晶粒是一个关键的问题。

图 3-22 Poly-Si TFT 转移特性曲线中的电流翘曲现象

图 3-23 晶界附近的电势分布和产生率分布曲线（漏端电压为 5V）

### 3.3.3 晶界处碰撞电离与 KINK 效应

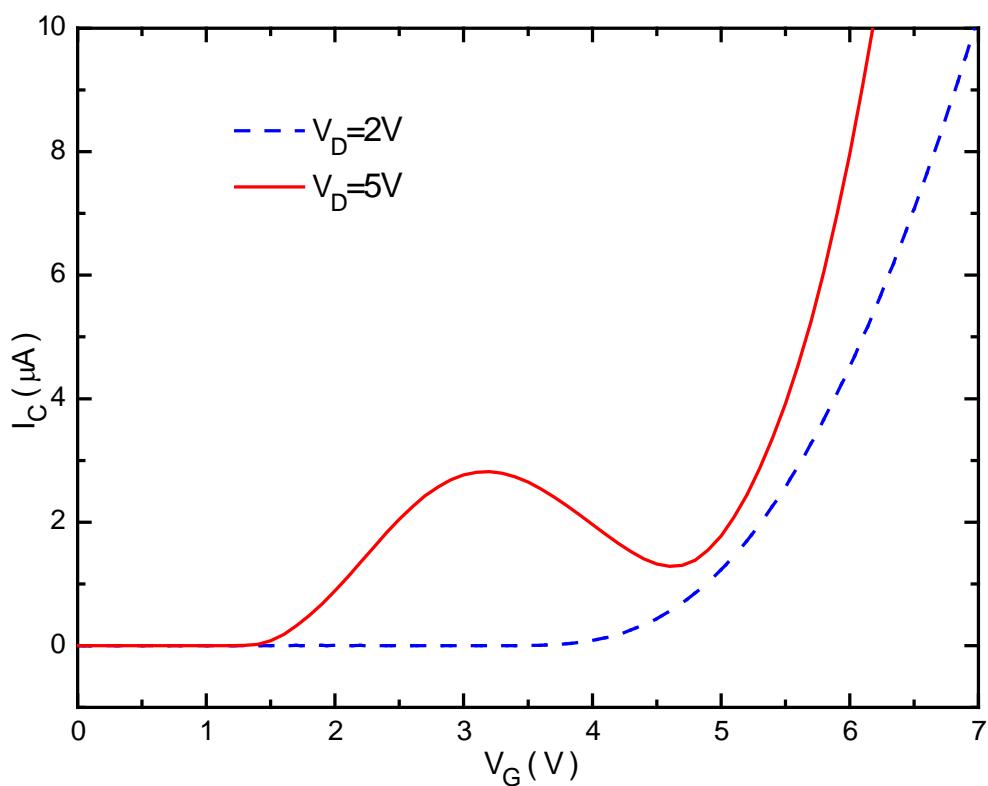

既然晶界处可能发生碰撞电离现象，则有可能通过晶界处的碰撞电离打开寄生晶体管的发射结，从而产生特殊的浮体现象。实际上，因为晶界一般不只是一个，晶界处发生碰撞电离的区域也就不止一个，这样，由晶界处的碰撞电离效应所引起的 KINK 效应便会是一个级联过程。图 3-24 示出了这一级联过程，如图 3-24 所示，这一级联过程可以看成是这样进行的：沟道电流  $I_0$  和复合一部分 ( $I_{R1}$ ) 后的注入电子电流  $I_{C1}$  在第一个晶界处发生碰撞电离，碰撞电离电  $I_{OM1} = (M_1 - 1) I_0$ ， $I_{CM1} = (M_1 - 1) I_{C1}$  和沟道电流  $I_0$  和再次复合一部分 ( $I_{R2}$ ) 后的注入电子电流  $I_{C2}$  又在第二个晶界处发生碰撞电离，引发碰撞电离电流  $I_{OM2} = (M_2 - 1)(I_0 + I_{OM1})$ ， $I_{CM2} = (M_2 - 1)(I_{C2} + I_{CM1})$ 。以此类推，每次碰撞电离产生的电流又会在下一个晶界处引发碰撞电离电流。可以预见，由晶界处碰撞电离开启的寄生晶体管的集电极电流将会强烈的受到栅压的影响，图 3-25 示出了寄生晶体管集电极电流随栅极电压的变化情况。

图 3-24 由 Poly-Si TFT 晶界处的碰撞电离引发的特殊 KINK 效应示意图

图 3-25 Poly-Si TFT 中寄生晶体管的集电极电流随栅极电压的变化曲线

如图 3-25 所示, 利用上述仿真结果可以得到集电极电流随栅压的变化曲线, 可以看到, 当漏端电压为 2V 时, 当栅压达到 4V 时, 寄生晶体管即会被晶界处发生的碰撞电离效应所开启; 当漏端电压为 5V 时, 当栅压较小时, 寄生晶体管会被漏端的碰撞电离效应所开启, 当栅压增大时, 一方面增多的电子会引发更强烈的碰撞电离, 另一方面增多的电子也会降低漏端的电阻和分压能力, 从而减弱漏端电场, 并最终使得漏端的碰撞电离效应减弱, 集电极电流下降, 但当栅极电压进一步增加时, 如前所述, 因为转移的电压降使得晶界处发生了碰撞电离, 故集电极电流又开始上升, 这充分表现了晶界处的碰撞电离导致的 KINK 效应的机制。

## 3.4 考虑 DIGBL 效应和晶界位置的晶界处势垒高度模型

### 3.4.1 表面势模型

如前所述, 晶界处势垒高度模型是晶界问题的核心问题, 也是建立大晶粒、少晶界 Poly-Si TFT 器件电流模型的核心问题。漏端电压在沟道内引发的电场会使得晶界势垒分布不对称, 造成面向漏端一侧的势垒被增高, 面向源端一侧的势垒现有的晶界处势垒高度模型被降低, 即发生 DIGBL 效应。由于一般情况下, 当器件工作在饱和区时, 漏端夹断区的电阻较高, 漏端电压主要降落于此, 使得夹断区内成为高场区, 当晶界处于此区时, 其位置越靠近漏端, DIGBL 效应将越明显, 面向源端一侧的势垒被降低的程度越大, 即 DIGBL 效应受晶界位置影响。现有的大多数模型要么无法反应 DIGBL 效应, 要么无法反应 DIGBL 效应受晶界位置影响的情况。Ho 等人利用电位叠加和镜像电荷方法考虑了 DIGBL 效应受晶界位置的影响, 在本节中, 本论文将采用求解准二维泊松方程并利用高斯定理的方法, 得到更为简洁的考虑了晶界位置对 DIGBL 效应影响的晶界处势垒高度模型。

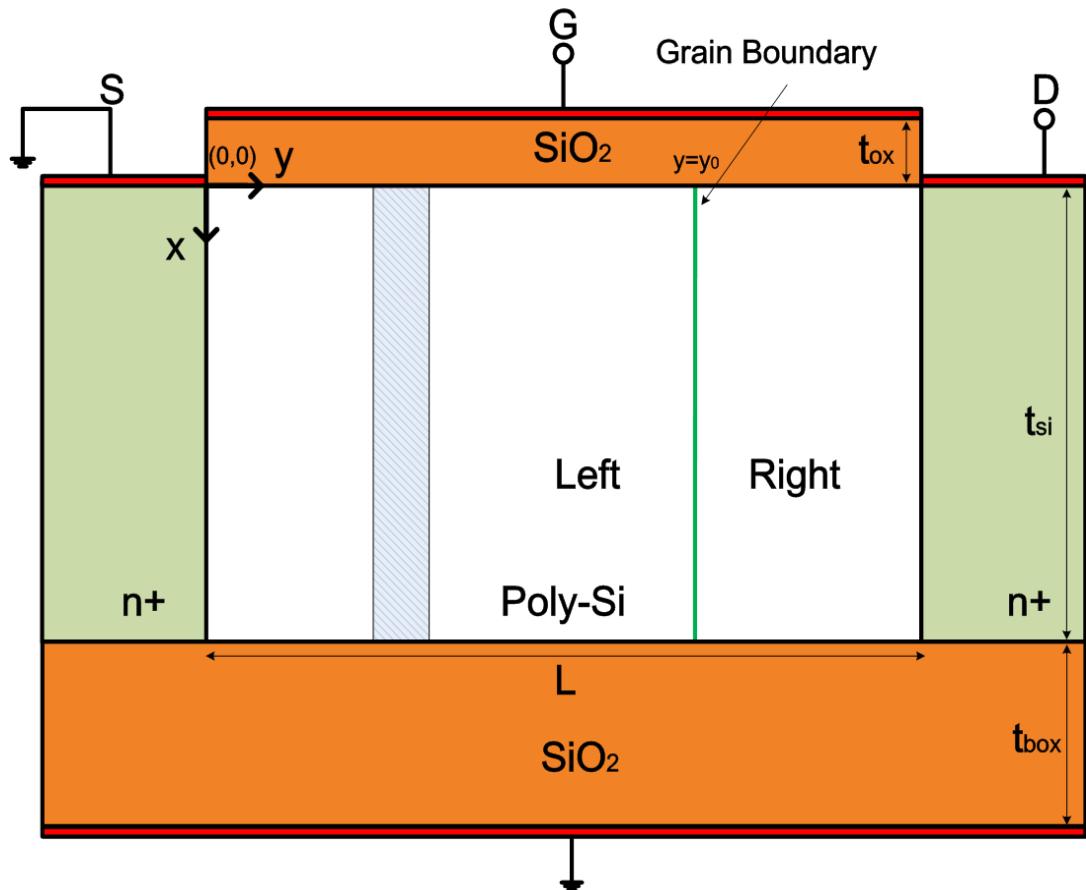

如图 3-26 所示, 我们采用全耗尽 Poly-Si TFT 器件, 栅氧层厚度为  $t_{ox}$ , 硅膜厚度为  $t_{si}$ , 沟道长度为  $L$ , 取 (0,0) 处为原点, 在  $y=y_0$  处放置一垂直于沟道方向的晶界, 此晶界将硅膜分成两个部分, 称之为左部和右部。现在在左部如阴影处所示, 取一个左上角顶点坐标为  $(0, y)$ , 长度为  $\Delta y$ , 高度为  $t_{si}$  的矩形区域, 并考虑对此区域使用高斯定理。

图 3-26 用于推导势垒高度模型的 Poly-Si TFT 示意图

设沟道表面  $(0, y)$  点的电势为  $V_s(y)$ , 则该点的电场为  $-dV_s(y)/dy$ , 对于  $x$  不为 0 的点  $(x, y)$ , 其电势将不同于  $(0, y)$  点, 现在将该矩形区域近似为等效高度为  $t_{si}/\eta$  的矩形, 其  $(x, y)$  点电势与  $(0, y)$  点相同, 为  $-dV_s(y)/dy$ , 则通过左边的电通量为  $(dV_s(y)/dy)(t_{si}/\eta)$ , 同理, 矩形右边的电通量为  $(-dV_s(y+\Delta y)/dy)(t_{si}/\eta)$ 。设器件的平带电压为  $V_{fb}$ , 栅电压为  $V_G$ , 则加在栅氧层两端的电压降为  $V_G - V_{fb} - V_s(y)$ , 电场大小为  $((V_G - V_{fb} - V_s(y))/t_{ox})$ , 在栅氧层和 Si 界面处, 电场将发生变化, 其大小为  $((V_G - V_{fb} - V_s(y))/t_{ox})(\epsilon_{ox}/\epsilon_{si})$ , 其中  $\epsilon_{ox}$ ,  $\epsilon_{si}$  分别为  $\text{SiO}_2$  和  $\text{Si}$  的介电常数, 则通过矩形上边的电通量为  $-((V_G - V_{fb} - V_s(y))/t_{ox})(\epsilon_{ox}/\epsilon_{si}) \Delta y$ , 忽略通过矩形下边的电通量, 则对等效矩形应用高斯定理可以得到:

$$\frac{dV_s(y)t_{si}}{\eta} - \frac{dV_s(y+\Delta y)t_{si}}{\eta} - \frac{V_G - V_{fb} - V_s(y)}{t_{ox}} \frac{\epsilon_{ox}}{\epsilon_{si}} \Delta y = \frac{-qN_a \Delta y t_{si}}{\eta \epsilon_{si}} \quad (3-5)$$

其中，方程式右侧考虑了等效矩形内由完全电离的电离受主提供的电荷，忽略了电子电荷。方程可整理成

$$\frac{1}{\eta} \frac{d^2 V_s(y)}{dy^2} + (V_G - V_{fb} - V_s(y)) \frac{C_{ox}}{t_{si} \epsilon_{si}} = \frac{qN_a}{\eta \epsilon_{si}} \quad (3-6)$$

其中， $C_{ox}=\epsilon_{ox}/t_{ox}$  为单位面积栅氧层电容。使用边界条件  $V_s(0) = V_{bi}$ ,  $V_s(y_0) = V_{s0}$ , 方程(3-6)可解为

$$V_s(y) = V_{ss} + \frac{(V_{bi} - V_{ss}) \sinh\left(\frac{y_0 - y}{l_0}\right) + (V_{s0} - V_{ss}) \sinh\left(\frac{y}{l_0}\right)}{\sinh\left(\frac{y_0}{l_0}\right)} \quad (3-7)$$

其中， $V_{ss} = V_G - V_{fb} - \frac{qN_a t_{si}}{\eta C_{ox}}$ ,  $l_0 = \sqrt{\frac{\epsilon_{si} t_{si}}{\eta C_{ox}}}$ 。式 (3-7) 即为器件左部表面势的近似表达式，同理，器件右部的表面势近似表达式为

$$V_s(y) = V_{ss} + \frac{(V_{s0} - V_{ss}) \sinh\left(\frac{L - y}{l_0}\right) + (V_{bi} + V_{DS} - V_{ss}) \sinh\left(\frac{y - y_0}{l_0}\right)}{\sinh\left(\frac{L - y_0}{l_0}\right)} \quad (3-8)$$

其中，使用了边界条件  $V_s(y_0) = V_{s0}$ ,  $V_s(L) = V_{bi} + V_{DS}$ 。

(3-7) 和 (3-8) 式中的  $V_{s0}$ , 即晶界处的表面势可以对晶界使用高斯定理得到，即

$$-\left(-\frac{dV_s(y_0)_{Left}}{dy}\right) \cdot \frac{t_{si}}{\eta} + \left(-\frac{dV_s(y_0)_{Right}}{dy}\right) \cdot \frac{t_{si}}{\eta} = \frac{-qN_t t_{si}}{\epsilon_{si} \eta} \quad (3-9)$$

其中，方程左侧考虑了晶界两边的电通量，右侧考虑了陷阱电荷，并假设它已被完全填充，浓度为  $N_t$ ，将 (3-7) (Left) 和 (3-8) (Right) 带入 (3-9) 可以得到：

$$V_{s0} = \frac{\frac{-qN_t}{\epsilon_{si}} \sinh\left(\frac{y_0}{l_0}\right) \sinh\left(\frac{L - y_0}{l_0}\right) + \left(\frac{V_{bi} - V_{ss}}{l_0}\right) \sinh\left(\frac{L - y_0}{l_0}\right) + \left(\frac{V_{bi} + V_{DS} - V_{ss}}{l_0}\right) \sinh\left(\frac{y_0}{l_0}\right)}{\sinh\left(\frac{L}{l_0}\right)} \cdot l_0 + V_{ss} \quad (3-10)$$

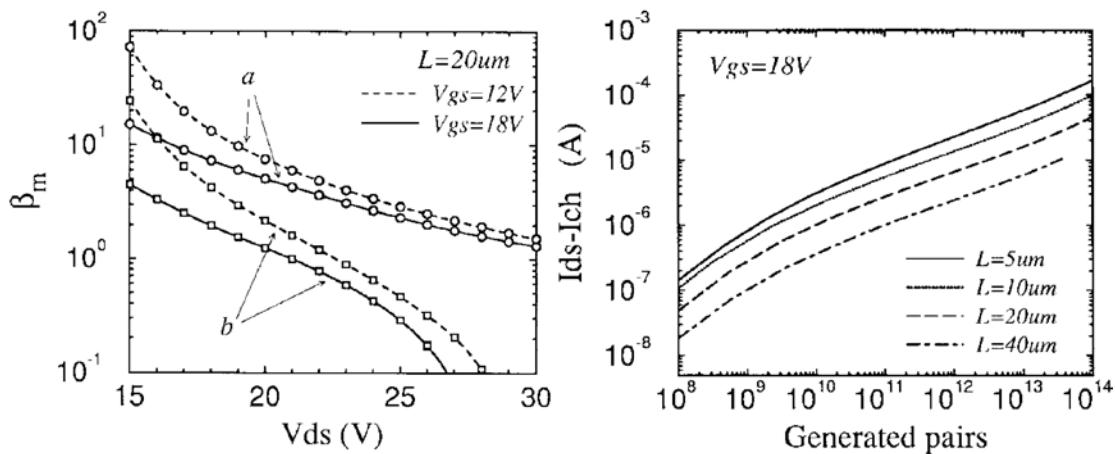

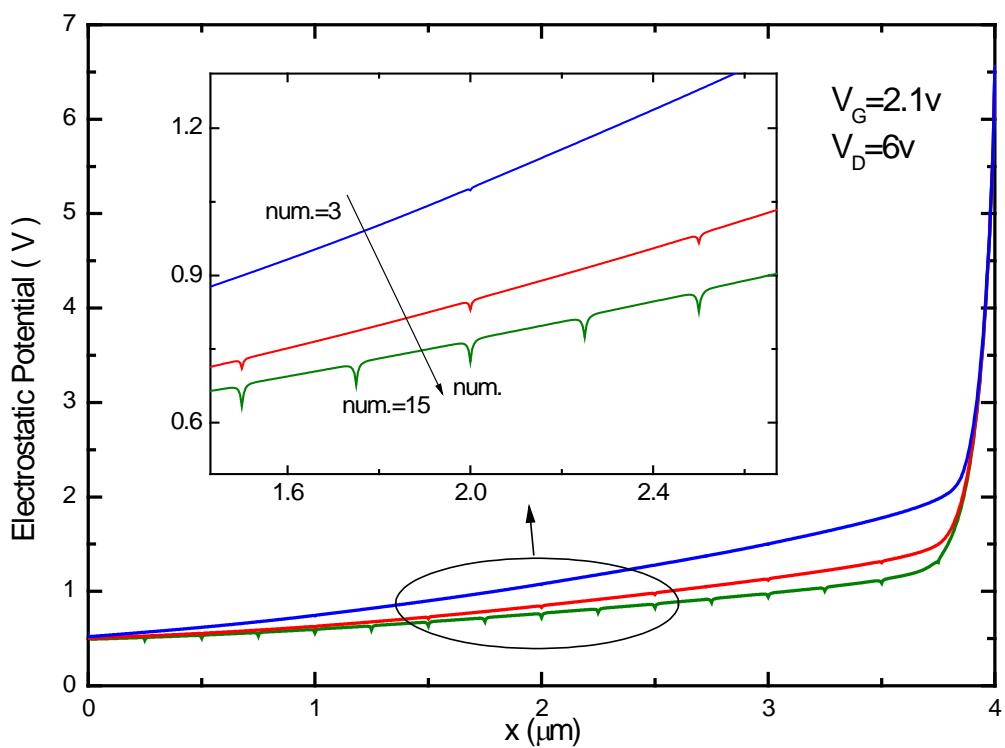

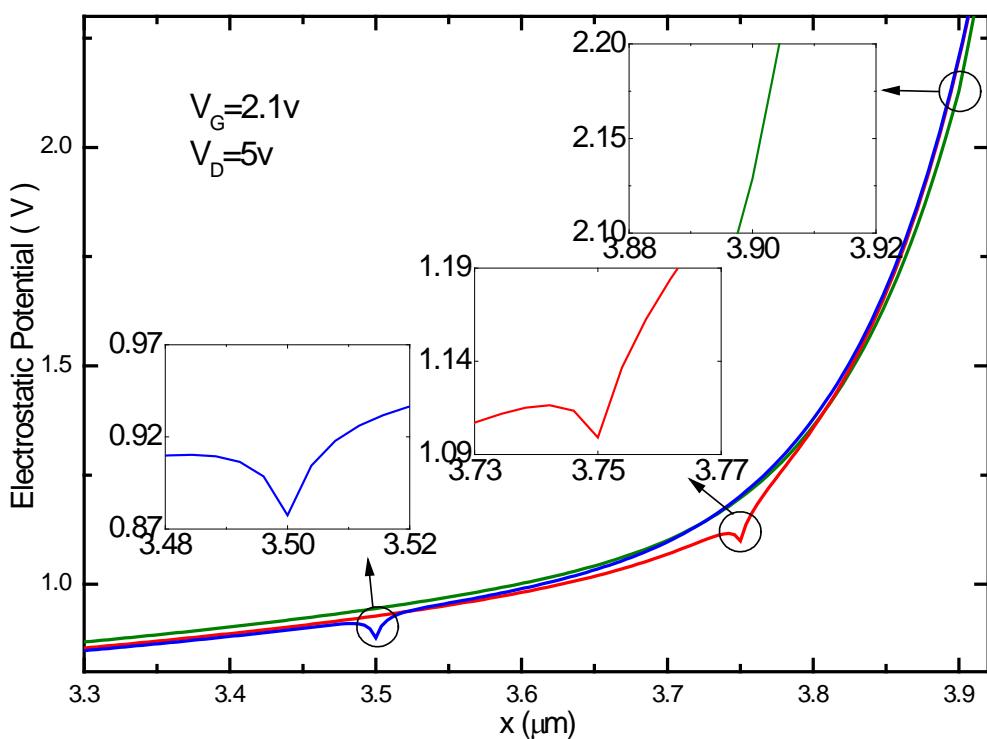

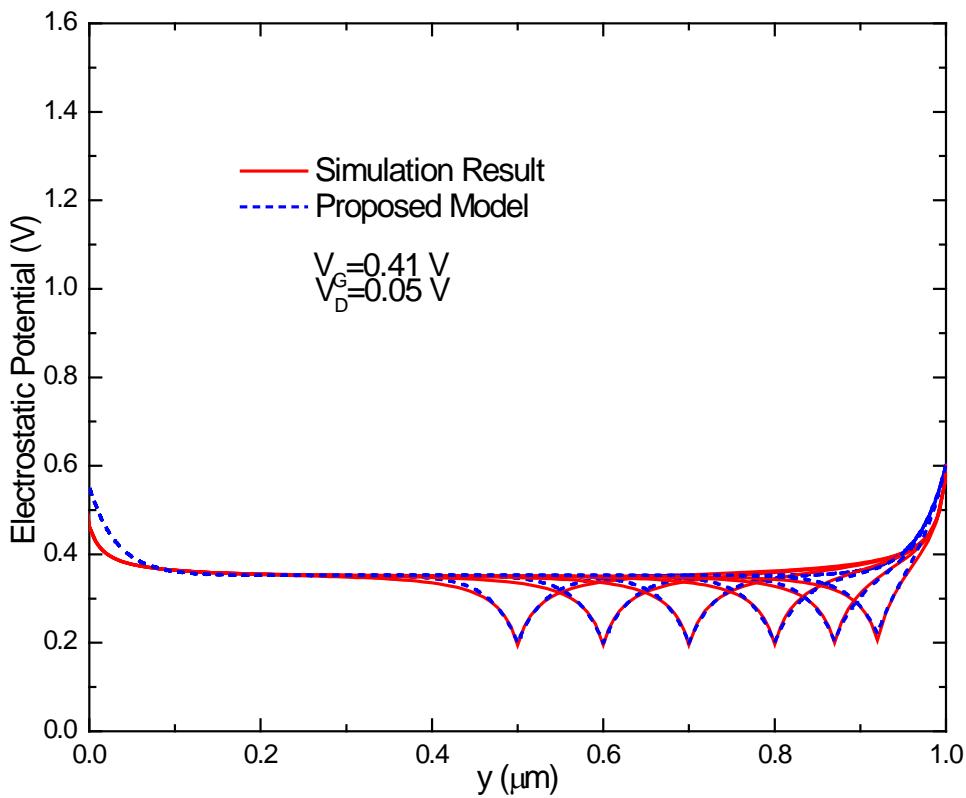

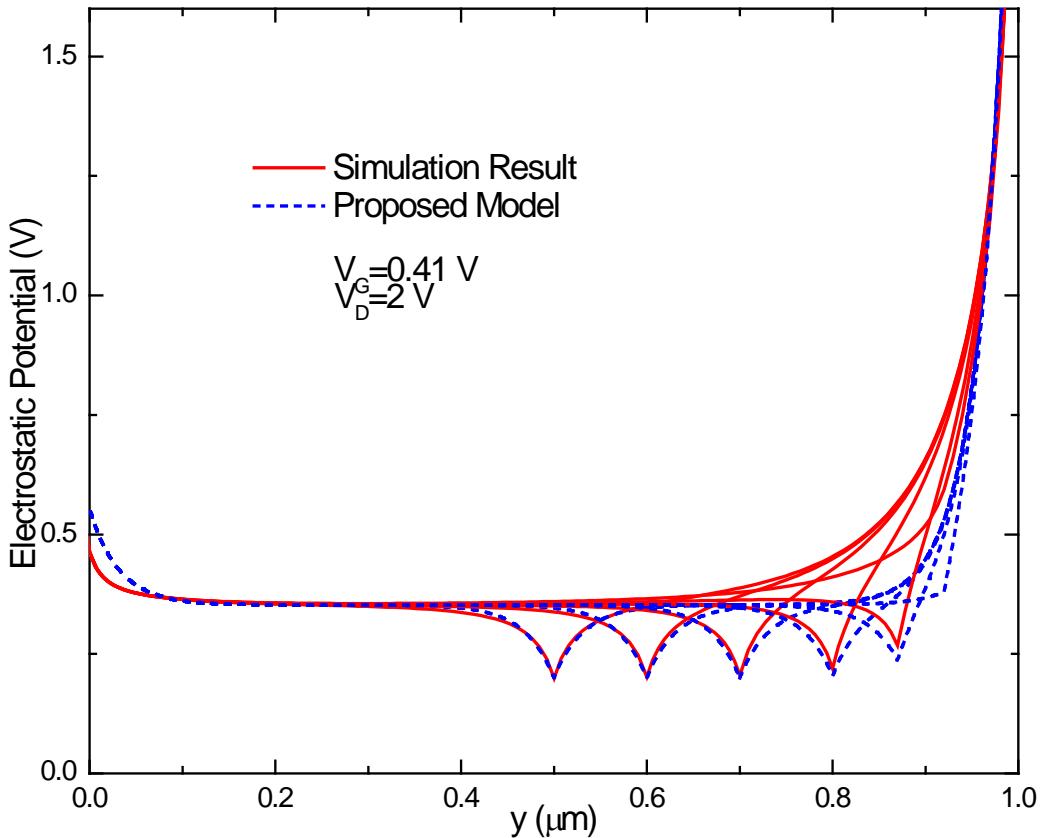

式 (3-7), (3-8), (3-10) 为只有一个晶界的 Poly-Si TFT 器件的表面势模型，图 3-27, 3-28, 3-29 使用 TCAD 仿真结果对模型进行了验证。

图 3-27 漏端电压为较小的  $V_D=0.05\text{V}$  时表面势模型的验证图 3-28 漏端电压为中等的  $V_D=1\text{V}$  时表面势模型的验证

图 3-29 漏端电压为较大的  $V_D=2\text{V}$  时表面势模型的验证

我们将使用 Sentaurus Device TCAD 对模型进行验证。这一次，我们在晶界上使用更为精确的指数分布的陷阱能级，两个施主能级（深禁态和带尾态）分布在能带的下方而两个受主能级分布在能带的上方，深禁态的陷阱浓度为  $2\times 10^{15}\text{cm}^{-2}$ ，特征能级分别距价带和导带  $0.11\text{eV}$  和  $0.08\text{eV}$ ，带尾态浓度为  $1\times 10^{16}\text{cm}^{-2}$ ，特征能级分别距价带和导带  $0.03\text{eV}$  和  $0.02\text{eV}$ 。施主和受主能级的电子的俘获横截面分别是  $1\times 10^{-17}\text{cm}^{-2}$  和  $1\times 10^{-15}\text{cm}^{-2}$ ，空穴的俘获横截面分别是  $1\times 10^{-15}\text{cm}^{-2}$  和  $1\times 10^{-17}\text{cm}^{-2}$ 。沟道长度为  $1\mu\text{m}$ ，栅氧层厚度为  $10\text{nm}$ ，硅膜厚度为  $100\text{nm}$ ，衬底掺杂为  $1\times 10^{16}\text{cm}^{-3}$ 。晶界位置分别取  $y=0.5, 0.6, 0.7, 0.8, 0.87, 0.92\mu\text{m}$ ，漏端电压分别取  $0.05, 1, 2\text{V}$ 。

如图 3-27 所示，当漏端电压很小时，仿真结果与解析模型符合的很好，模型可以反映表面势随晶界位置的变化。我们可以看到，由于漏端电压较小，且并未在漏端形成高电场区，从而 DIGBL 效应并不明显，晶界两边势垒基本呈对称分布，且其随位置的改变也不明显。如图 3-28 所示，当漏端电压增大时，仿真结

果和模型符合的很好, DIGBL 效应开始出现, 在靠近漏端的晶界上我们可以看见, 面向源端的势垒高度开始降低, 面向漏端的势垒高度开始增加, 并且, DIGBL 效应随位置的变化也可以被模型表现出来, 即当晶界更靠近漏端时, 其面向源端的势垒被降低的更多。如图 3-29 所示, 当漏端电压进一步增加时, 模型与仿真结果符合的较好, 并且可以看到, 离漏端最近的晶界的势垒已经在强电场的作用下消失, 模型很好的反映了 DIGBL 效应及其受晶界位置的影响。基于表面势模型, 我们可以得到势垒高度的模型。

### 3.4.2 势垒高度模型

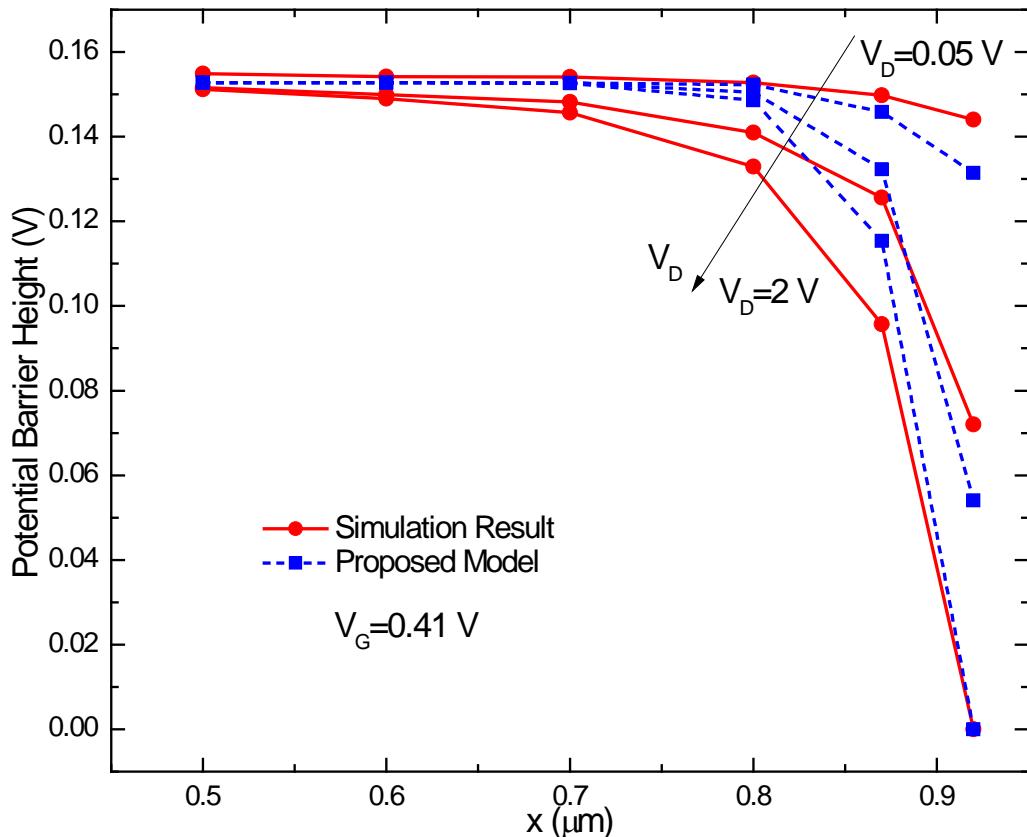

如图 3-27-图 3-29 所示, 我们将势垒高度定义为

$$\Delta V = V(y') - V_{s0} \quad (3-11)$$

其中,  $y'$  点是曲线的拐点, 则

$$V''_s(y') = \frac{\frac{1}{l_0^2}(V_{bi} - V_{ss})\sinh\left(\frac{y_0 - y'}{l_0}\right) + \frac{1}{l_0^2}(V_{s0} - V_{ss})\sinh\left(\frac{y'}{l_0}\right)}{\sinh\left(\frac{y_0}{l_0}\right)} = 0 \quad (3-12)$$

从而

$$(V_{bi} - V_{ss})\sinh\left(\frac{y_0 - y'}{l_0}\right) + (V_{s0} - V_{ss})\sinh\left(\frac{y'}{l_0}\right) = 0 \quad (3-13)$$

则由 (3-7) 式有  $V(y') = V_{ss}$ , 将其带入 (3-11), 并利用 (3-10) 式可得:

$$\Delta V = \frac{\frac{qN_t l_0}{\varepsilon_{si}} \sinh\left(\frac{y_0}{l_0}\right) \sinh\left(\frac{L - y_0}{l_0}\right) - (V_{bi} - V_{ss}) \sinh\left(\frac{L - y_0}{l_0}\right) - (V_{bi} + V_{DS} - V_{ss}) \sinh\left(\frac{y_0}{l_0}\right)}{\sinh\left(\frac{L}{l_0}\right)} \quad (3-14)$$

此即为含有一个晶界的 Poly-Si TFT 势垒高度模型。图 3-30 利用 Sentaurus Device TCAD 验证了势垒高度模型。可以看到模型与仿真结果符合的很好, 最大绝对误差不超过 0.02V, 且能够反映 DIGBL 效应受晶界位置的影响, 即晶界越靠近漏端, 势垒高度越低, 尤其在大的漏端电压情况更为明显。

图 3-30 势垒高度模型的验证

综上所述，本节采用求解准二维泊松方程并利用高斯定理的方法，求解了具有一个晶界的 Poly-Si TFT 的表面势模型和势垒高度模型，通过 TCAD 仿真验证，模型对不同的晶界位置和电压大小均具有很好的精度，可以预测 DIGBL 效应及其受晶界位置变化的影响。相比于 Ho 的模型，本节所采用的推导方法更简单，得到的模型更简洁，同时具有很高的精度，有助于 DIGBL 效应和离散晶界效应的研究，有助于 Poly-Si TFT 电流传导模型的建立。

### 离散晶界效应研究小结

本章利用 TCAD 仿真工具和物理建模方法对 Poly-Si TFT 的离散晶界效应进行了研究，得到了创新性的结论。首先，本章通过分析晶界上陷阱浓度、晶界数目和晶界位置对晶界处势垒高度的影响提出并解释了晶界上陷阱浓度越少、晶界数目越少、晶界位置越靠近漏端，晶界处势垒高度便越低，导致器件寄生晶体管集电极电流和 KINK 效应越大，同时分析了它们对寄生晶体管效应和碰撞电离效应

的影响。这些结论指出对于大晶粒、少晶界、少陷阱的现代 Poly-Si TFT 器件，更要注意 KINK 效应所带来的影响，同时，器件的不均匀性将会影响其性能，必须控制；其次，本章首次研究了 Poly-Si TFT 中晶界处的碰撞电离现象，指出正是由于栅压的影响，原本加在漏端高阻区的电压降会被高栅压转移到晶界靠近漏端一侧的空间电荷区上，从而引起晶界处碰撞电离效应，产生碰撞电离电流并引起特殊的 KINK 效应；最后，本章利用高斯定理，得到了考虑 DIGBL 效应和晶界位置影响的表面势和势垒高度模型，推导过程简单，模型结果准确而简洁，为进一步得到考虑晶界位置影响的 Poly-Si TFT 传导电流模型提供了基础。

## 第四章 用于面板的无畸变传输线研究

在现代电路设计中，由互连线带来的信号完整性问题已经变得越来越重要。对于面板设计，随着显示尺寸和分辨率的提高，由栅信号线和数据线延迟导致的图像显示失真等问题越来越严重，严重制约了 Poly-Si TFT 面板向大尺寸、高分辨率方向的发展。为解决线上延迟问题，人们提出了很多设计方法，而本章将提出利用无畸变传输线的新方法。无畸变传输线是一种满足 Heaviside 条件的传输线，其上传输的不同频率信号的振幅衰减和传播速度均相同，大大减弱了信号的畸变程度和信号延迟，具有在面板中应用的潜力。本章将针对栅极信号延迟问题提出解决方法，采用无畸变传输线设计栅极扫描线，使得线上信号畸变大大减小，从而减小信号延迟并增强面板电路的信号完整性，同时，本章还将提出一种新的利用线间互电容和互电感的无畸变传输结构-LC 线。

### 4.1 面板的信号完整性问题简述

#### 信号完整性问题

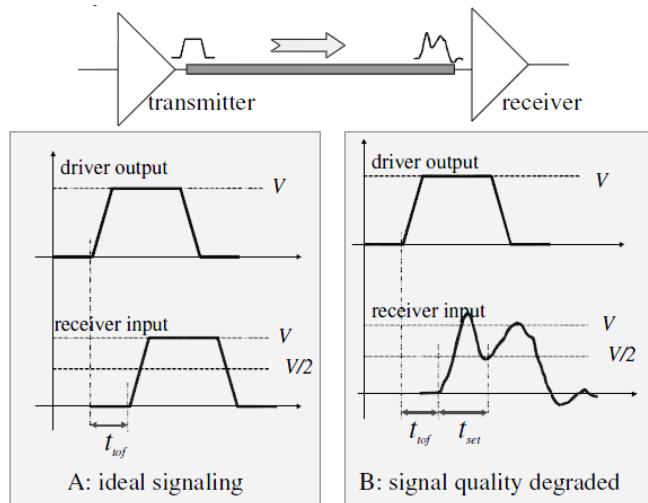

对于现代电路设计技术来说，解决由互连线带来的传输信号质量问题已经变得越来越重要。实际上，对于深亚微米（Deep Submicron, DSM）片上系统（System on Chip, SOC）来说，互连线已经开始代替晶体管，成为电路功耗、延迟等关键参数的决定性因素<sup>[84]-[92]</sup>。为此，甚至已经出现了以互连为中心的设计方法，并出现了片上网络（Network on Chip, NOC）的概念。信号完整性问题即是指信号在互连线上传输的质量问题。图 4-1 给出了信号完整性问题的示意图<sup>[88]</sup>，当信号从发送端通过互连线传输到接收端时，在理想情况下，只会有大小为飞行时间（Time of Flight, TOF）的延迟出现。但在实际情况中线上传输的信号则会受到色散、串扰、电源、衬底耦合以及传输线效应等影响而改变特性，可能出现更大的延迟，并且只有稳定在一定范围内一定时间后（置位时间，Setting Time）才会被接收，从而影响了时序。同时，信号的振幅大小也可能被改变，如果信号质量过差而导致接收端无法判断，甚至可能会引发错误。

图 4-1 信号完整性问题示意图<sup>[88]</sup>

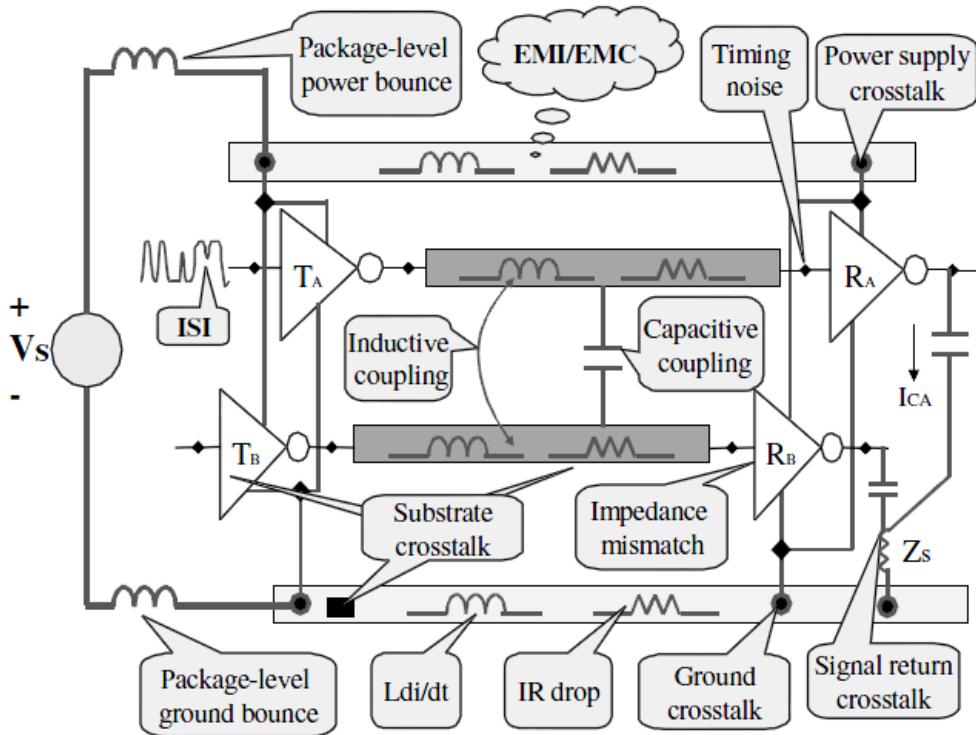

信号完整性问题主要包括噪声问题与延迟问题。噪声是指信号受到干扰后相对于理想值的偏移，常见的噪声包括器件噪声、电源噪声、线间串扰、衬底耦合、传输线终端反射、信号间干扰（Inter Symbol Interference, ISI）以及电磁干扰等，如图 4-2 所示<sup>[88]</sup>。其中，互连线间通过电感和电容的耦合而产生的串扰、传输线因为终端阻抗不匹配而产生的反射以及因为信号色散而引起的 ISI 等问题将会在本章及下一章中进行详细阐述并提出分析、解决和利用的办法。

信号的延迟主要是由互连线上的分布电阻、电容和电感引起的。随着器件尺寸的减小，由互连线引起的信号延迟已经超过了器件，成为集成电路速度的主要限制因素。集成电路中的互连线基本上可以分成两类，一类是局域互连线，这些互连线在逻辑单元内部连接着有源器件，当工艺特征尺寸减小时，这些互连线上的延迟也将减小，这主要是因为器件间的距离变短了。另一类互连线是全局互连线，他们连接着不同的逻辑单元（如总线）或者在整个芯片上分布信号（如时钟网络），这些互连线的延迟将随着工艺制程的进步而增大，这是因为不仅互连线横截面积减小了、互连线电阻增加了，而且芯片尺寸也增加了、全局互连线变长了。对于较长的互连线，必须对其延迟问题充分重视，在面板中，用于逐行扫描的栅极互连线以及用于输入信号的源端互连线是长互连线，而且随着显示屏幕的增大和像素的增多，解决其信号延迟问题将越来越重要，下面将对面板中延迟问题进行具体分析。

图 4-2 电路中常见的噪声源<sup>[88]</sup>

### 面板中的信号延迟问题

Poly-Si TFT 以其高迁移率等特性可用于大面积、高分辨率平板显示，并可集成显示单元与周边驱动电路。随着显示尺寸和分辨率的提高，由栅信号线和数据线延迟导致的图像显示失真问题越来越严重，同时，对于由 Poly-Si TFT 构成的周边驱动电路，由于其相对于单晶硅较低的导通能力，也会引起信号的延迟和失真。如若栅信号延迟过于严重，不能保证在选通时段内将 TFT 完全打开，则像素电容不能被充分充电，便会导致图像失真。信号延迟和失真制约了 Poly-Si TFT 面板向大尺寸高分辨率方向的发展。

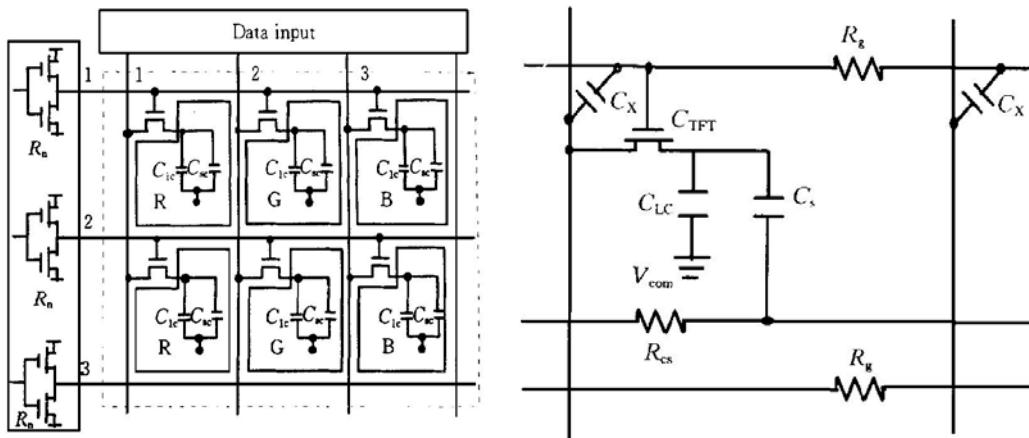

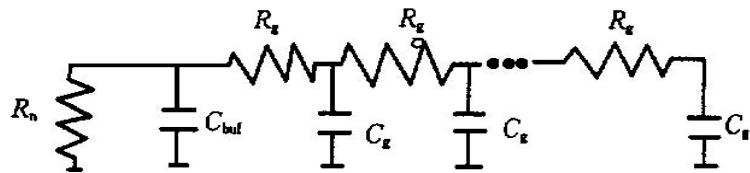

面板中的延迟主要是由 TFT 和互连线的电阻和电容带来的，如图 4-3 左所示，对于分辨率为  $M \times N$  的显示电路，栅线为  $M$  行，数据线为  $3N$  条， $R_n$  为栅驱动电路中缓冲寄存器开态电阻， $C_{buf}$  为其寄生电容；如图 4-3 右所示， $R_g$  为一个像素的栅线电阻， $C_g = C_{TFT} + C_x$  为一个像素的栅线电容， $C_{TFT}$  为 TFT 沟道电容， $C_x$  为栅信号线和数据线间电容，则一条栅线可以用如图 4-4 所示的模型来表示，电阻和电容带来了信号畸变，畸变导致了延迟现象<sup>[93][94]</sup>。

图 4-3 Poly-Si TFT 面板示意图<sup>[93][94]</sup>图 4-4 Poly-Si TFT 面板栅信号线模型<sup>[94]</sup>

### 解决面板信号延迟问题的技术

为解决面板中的延迟问题，人们提出了许多技术，从器件结构和电路设计上来减少互连线上的延迟，增强信号完整性。Gleskova 等人通过在玻璃衬底中打孔（Via Hole）的方法来减少栅信号延迟<sup>[95][96]</sup>，即通过在玻璃衬底中打孔，使得栅线（gate line）与玻璃衬底另一侧上的一条总线（back line）连接起来，如图 4-5 上图所示。图 4-5 下图所示为 via hole 方法的等效电路，它可以看做是经过变化的 RC 传输线，是多个两端网络的级联。通过仿真可以发现，当另一侧总线的电阻越小、所打的孔洞越多时，延迟就会越小，并且，栅线中的最大延迟可以表示成  $T_m = mRCN^2$ ，其中，R 和 C 分别是像素的电阻和电容，N 为一排像素的个数，m 是一个与所打的孔洞数 L 以及栅线电阻与衬底另一侧总线电阻比值 K 有关的值，经由 SPICE 仿真可以得到 m 值曲线，显然 L 值和 K 值越大，延迟越小。当 L=2 而 K=10 时，m 值为 0.05 左右，与传统的 RC 传输线的 0.38 左右相比，Via Hole 方法可以减少栅线的延迟到原来的 1/7 至 1/8。尽管如此，Gleskova 等人并没有给出实验中延迟减小的数据，也没有给出关于 via hole 方法更多的理论依据。

图 4-5 Via Hole 方法结构示意图和等效电路<sup>[95][96]</sup>

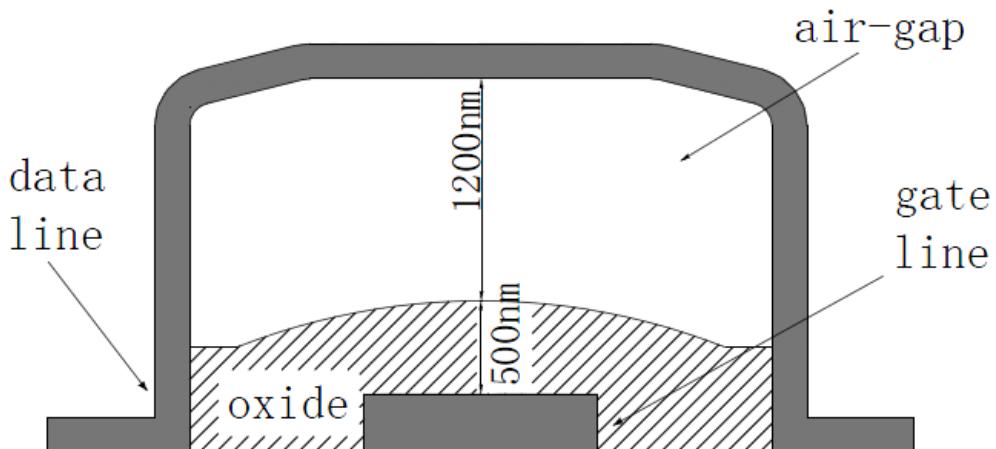

Park 等通过改进数据线与栅线间的结构,以减少交叉电容的方式减少了数据线的延迟<sup>[97][98]</sup>。在栅线与数据线交叉处,传统的工艺引入了氧化层,这使得交叉处产生了较大的电容,Park 等将空气间隙加入到传统结构,形成了如图 4-6 所示的空气桥结构 (Air Bridge),因为空气的介电常数很低,使得交叉处的电容降低,从而使数据线信号延迟降低了 10 倍左右。进一步,Park 等又提出凹空气桥结构 (Recessed Air Bridge),如图 4-7 所示,在这种结构中,空气间隙位于氧化层之下,这样在保证延迟减小的同时也保证了机械强度。此外,还有许多方法被用来减少面板的线上延迟,如 Chen 等通过对驱动电路进行优化来解决数据线上的信号延迟问题等<sup>[99]</sup>。

图 4-6 空气桥结构及其对信号延迟的减少<sup>[97]</sup>图 4-7 凹空气桥结构及其对信号延迟的减少<sup>[98]</sup>

## 4.2 无畸变传输线简述

### 互连线与传输线

无畸变传输线是 Cheng 等为改变互连线线上信号完整性而提出的一项传输线技术，本章第三节将利用此项技术改善面板中的延迟问题，在此之前，本节先对此项技术做一简述并对其理论基础做简单分析。

如前所述，全局互连线因为其延迟和功耗等问题成为了现代 SOC 性能的制约因素。以前，人们用插入缓冲器的方法来改善这一问题，然而这一方法并不能真正解决问题，因为它们占用了过多的面积并且功耗很大，同时他们也将影响芯

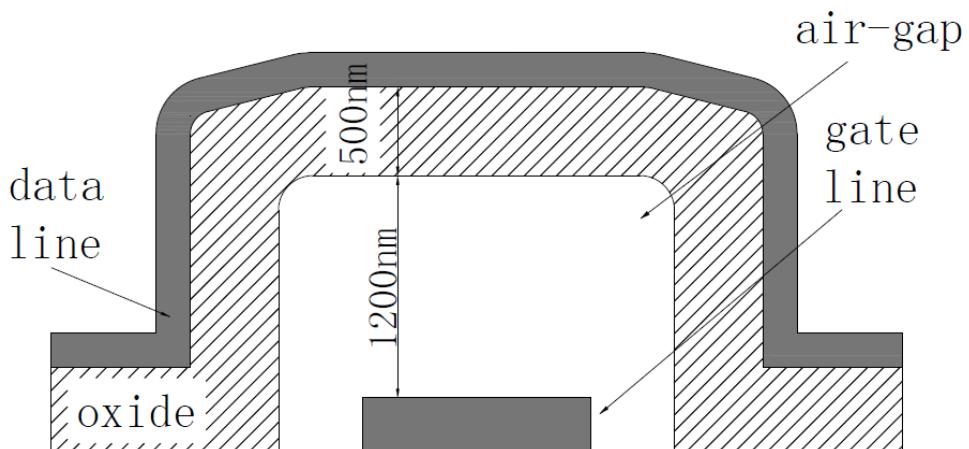

片的布线布局并带来噪声。为解决互连线所带来的问题，传输线被越来越多的应用到实际中来<sup>[100]-[103]</sup>，在传输线上，信号以电磁波的方式进行传播，信号传播的速度很快，他们在介质中以光速传播，信号消耗的功率又很少，因为电磁波的传播并不需要传输过程中的驱动器。为形成传输线并控制传输线上的电感，一些用于片上(On Chip)级的传输线结构如图4-8左所示，它们分别是(a)单端微波传输带，(b)差分微波传输带，(c)单端传输带，(d)差分传输带，以及(e)共面线。

然而，使用传输线作为互连线虽然有速度和功耗方面的优势，但也有问题需要解决，其中，最重要的是信号畸变问题。一般而言，由于传输线上的分布电阻、电容和电感，不同频率的波在其上传输时无论是振幅衰减大小，还是传输速度都不一样，高频信号传播速度快而衰减大，低频信号传播速度慢而衰减小，这样，对于一个在输入端一般的信号方波，由于信号频谱很宽，信号内各频率的波经过不同的衰减以不同的速度到达接收端时，接收端的信号将会畸变很大，这些畸变的信号还会影响后续的信号，形成信号间干扰(Inter-Symbol Interference, ISI)。为减少这一畸变，人们曾提出很多方法<sup>[104]-[110]</sup>，Dally等通过在发射机处做预先处理来补偿高频损失<sup>[104]</sup>，Ho等利用周期放电方案来减少依赖于信号的延迟变化<sup>[105]</sup>，Afshari等利用可变电容来减少色散和衰减<sup>[106]</sup>，Flynn等利用电阻负载来控制ISI<sup>[109]</sup>。无畸变传输线是Cheng等提出的<sup>[112]-[115]</sup>，他们利用插入电导的方法使得传输线上的分布电阻、电容、电感和电导满足Heaviside条件，从而使得传输线上的信号传输速度和衰减大小不依赖于信号频率，实现信号的无畸变传输。以下先简单分析一下无畸变传输线的基本原理。

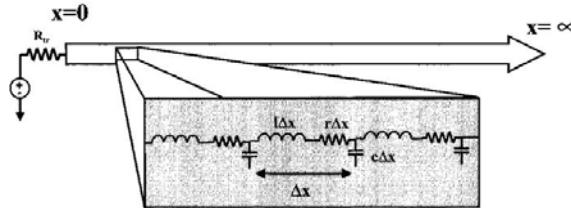

图4-8 片上级传输线结构及其分布式模型<sup>[114]</sup>

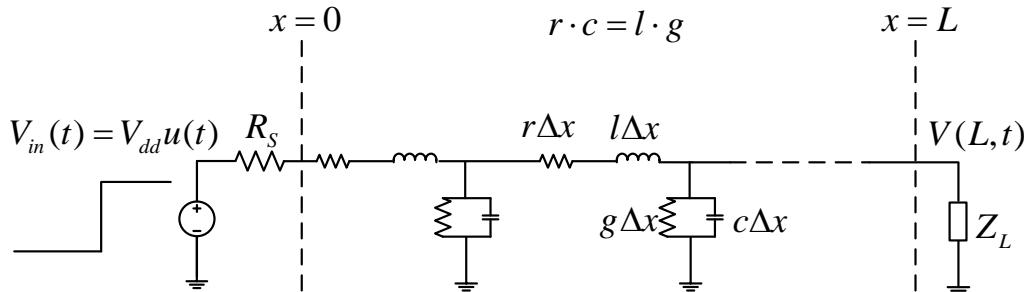

## 无畸变传输线基本理论

无论是对于片上级、封装级还是板级传输线，电报方程（telegrapher's equations）都是其理论基础<sup>[114]</sup>。对于传输线上的分布电阻 R，电容 C，电感 L 和电导 G，若取其上一小段  $\Delta z$ ，则等效电路如图 4-8 右所示。电报方程描述了传输线上电压和电流随距离 z 和时间 t 的变化关系：

$$\frac{\partial V(z, t)}{\partial z} = -RI(z, t) - L \frac{\partial I(z, t)}{\partial t} \quad (4-1)$$

$$\frac{\partial I(z, t)}{\partial z} = -GV(z, t) - C \frac{\partial V(z, t)}{\partial t} \quad (4-2)$$

电报方程的一般解是

$$V(z) = V^+(z) + V^-(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z} \quad (4-3)$$

由分别沿 z+ 方向和 z- 方向传播的波组成，以沿 z+ 方向的波为例

$$V^+(z) = V_0^+ e^{-\gamma z} = V_0^+ e^{-\alpha z - j\beta z} \quad (4-4)$$

其中  $\gamma$  为传播常数

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)} \quad (4-5)$$

$\alpha$  为衰减因子，经过衰减后的波的振幅为

$$A(z) = V_0^+ e^{-\alpha z} \quad (4-6)$$

$\beta$  为相位常数， $\omega$  为信号频率，波的传播速度为

$$v = \frac{\omega}{\beta} \quad (4-7)$$

特征阻抗  $Z_0$  被定义为

$$Z_0 = \frac{V^+(z)}{I^+(z)} = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \quad (4-8)$$

不同的 R, L, C, G 将带来不同的  $\gamma$ ,  $\alpha$ ,  $\beta$  值和不同的传输线性质。

对于片上级传输线，因为二氧化硅绝缘性非常好，故 G 可近似为 0，此时，对于不同的频率，传输线将表现出不同的性质，若信号频率很低， $\omega L \ll R$ ，则

$$\begin{aligned} \gamma &= \alpha + j\beta = \sqrt{j\omega RC} \\ &= \sqrt{\frac{\omega RC}{2}} + j\sqrt{\frac{\omega RC}{2}} \end{aligned} \quad (4-9)$$

$$\alpha = \sqrt{\frac{\omega RC}{2}} \quad (4-10)$$

$$v = \frac{\omega}{\beta} = \sqrt{\frac{2\omega}{RC}} \quad (4-11)$$

可以看到，当信号频率很低时，衰减因子和相速度均为频率的函数，频率越低，衰减越小而速度越低。我们把这种工作区域成为 **RC** 区域，一般而言，10GHz 以下的情况属于这个区域。

当频率更高时，使得  $\omega L >> R$ ，则

$$\begin{aligned} \gamma &= \alpha + j\beta = \sqrt{(R + j\omega L)j\omega C} \\ &= \frac{R}{2\sqrt{L/C}} + j\omega\sqrt{LC} \end{aligned} \quad (4-12)$$

$$\alpha = \frac{R}{2\sqrt{L/C}} = \frac{R}{2Z_0} \quad (4-13)$$

$$v = \frac{\omega}{\beta} = \frac{1}{\sqrt{LC}} = \frac{c_0}{\sqrt{\epsilon_r}} \quad (4-14)$$

其中  $c_0$  为真空中的光速， $\epsilon_r$  为介电常数。可以看到，此时衰减和相速度均和频率无关，我们称此工作区域为 **LC** 区域。可见，通过设计，使得传输线工作在 **LC** 区域是减少畸变的一种方法。

现在，我们来考虑一种特殊情况，即片上分布电阻  $R$ 、电容  $C$ 、电感  $L$ 、电导  $G$  满足如下关系式：

$$\frac{R}{G} = \frac{L}{C} \quad (4-15)$$

则有

$$\begin{aligned} \gamma &= \alpha + j\beta = \sqrt{(R + j\omega L)(RC/L + j\omega C)} \\ &= \frac{R}{\sqrt{L/C}} + j\omega\sqrt{LC} \end{aligned} \quad (4-16)$$

$$\alpha = \frac{R}{\sqrt{L/C}} = \frac{R}{Z_0} \quad (4-17)$$

$$v = \frac{\omega}{\beta} = \frac{1}{\sqrt{LC}} = \frac{c_0}{\sqrt{\epsilon_r}} \quad (4-18)$$

$$Z_0 = \sqrt{\frac{L}{C}} \quad (4-19)$$

可见，此时在任何频率下，信号的衰减和速度将不再与频率相关，信号以光速传播，特征阻抗变为纯电阻。**(4-15)** 式被称为 Heaviside 条件，当满足 Heaviside 条件时，传输线上信号的传输与频率无关，信号不发生畸变。在片上级传输线设计中，可以通过材料和结构上的改进，使得 Heaviside 条件被满足来实现无畸变传输线。

### 无畸变传输线的应用

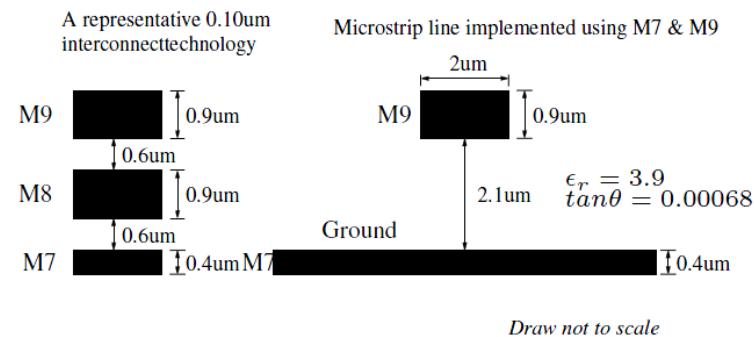

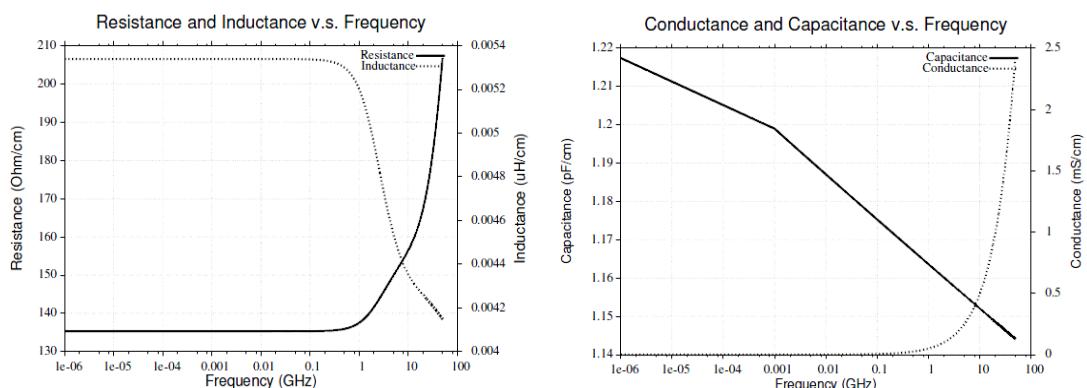

基于无畸变传输线理论，Cheng 等通过插入电导来满足 Heaviside 条件的方法来实现无畸变传输线<sup>[112]-[115]</sup>。他们选择的传输线基本结构为如图 4-9 所示的单端微波传输带。为插入电导，以满足  $RC=LG$ ，必须首先确定  $RLC$  的值。而实际上， $R$ ,  $L$ ,  $C$  本身是随频率变化的值，如图 4-10 所示，当频率增大时，由于趋肤效应，电流会集中在互连线表面进行传导，这使得互连线电阻显著增加，而电感下降，与此同时，电容的变化量很小，电导的变化量和电阻相比也是很小的。

图 4-9 Cheng 等用于改造的单端微波传输带结构参数<sup>[114]</sup>

图 4-10 电阻、电感、电容和电导对频率的变化曲线<sup>[114]</sup>

图 4-11 采用插入电导方法构成的无畸变传输线的结构及功能<sup>[114]</sup>

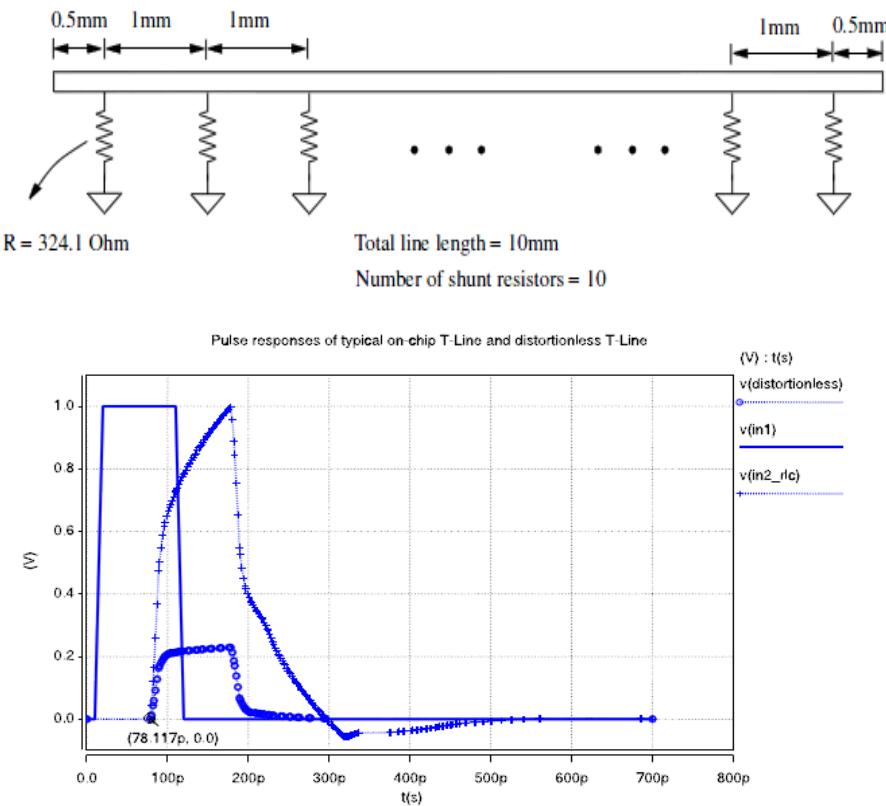

由上一小节的分析我们可以知道, 衰减和相速随频率的变化主要发生在低频时, 在高频时它们与频率无关, Cheng 等基于这一原理, 在选择插入的电导值时, 采用了在低频时匹配 (match at DC) 的方法, 由图 4-10 可知, 在 DC 时,  $R=135.3\Omega/\text{cm}$ ,  $C=1.22\text{pF/cm}$ ,  $L=5.34\text{nH/cm}$ , 则插入的电阻大小为  $L/(RC)=32.41\Omega/\text{cm}$ 。在实际插入电导时, 显然插入的电导数目越多, 传输线越接近分布系统, 但这同时也会增加占用面积, 但实际上, 插入电导的间距只要小于一定值即可达到需要的信号特性。如图 4-11 上图所示, 对于 1cm 的 Cu 传输线, Cheng 等插入的电导数为 10 个, 所得到的波形结果如图 4-11 下图所示, 可以看到, 信号的上升延迟被大大减小了, 信号下降的延迟-“长尾巴”也基本消失, 这意味着信号的完整性被大大改善, 延迟被显著减小, ISI 因而得到很好的抑制。但同时也看到, 通过无畸变传输线的波形虽然不会畸变, 但振幅会降低, 而在接收端的现代传感放大器足可以解决这个问题。为减少电压降低, 稳态电压的分析至关重要, 本论文将在第五章具体分析这一问题。此外, 无畸变传输线抗串扰和噪

声，因为它被屏蔽的很好，并且未加入缓冲器。除了在片上的应用外，Cheng 等还将无畸变传输线的应用领域扩展到了封装领域，也取得了减少信号畸变和 ISI，增强信号完整性的效果。Cheng 等还提出了用于无畸变互连线设计的眼图模型，本论文第五章将给出无畸变传输线的基于物理的时域解析模型，以分析并设计无畸变传输线。

综上所述，无畸变互连线由于基本满足了 Heaviside 条件，其上传输的不同频率信号的振幅衰减和传播速度相同，从而使得信号的畸变程度得以大大减弱，有效的减少了信号延迟，增强了信号完整性，具有在面板中应用的潜力。在下一节，本论文将采用无畸变传输线技术设计栅极扫描线，针对栅极信号延迟问题提出解决方法。

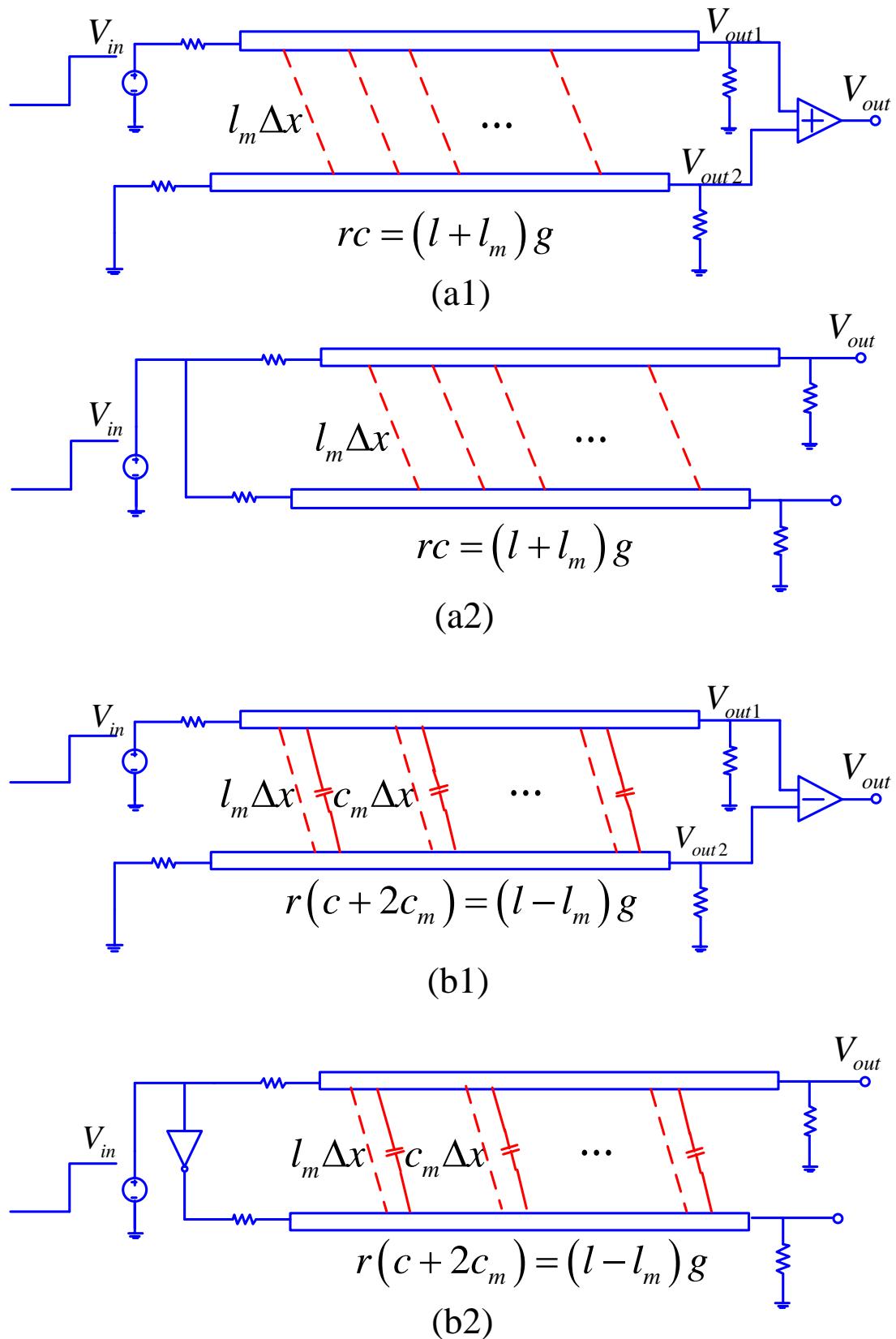

## 4.3 无畸变传输线在面板中的应用

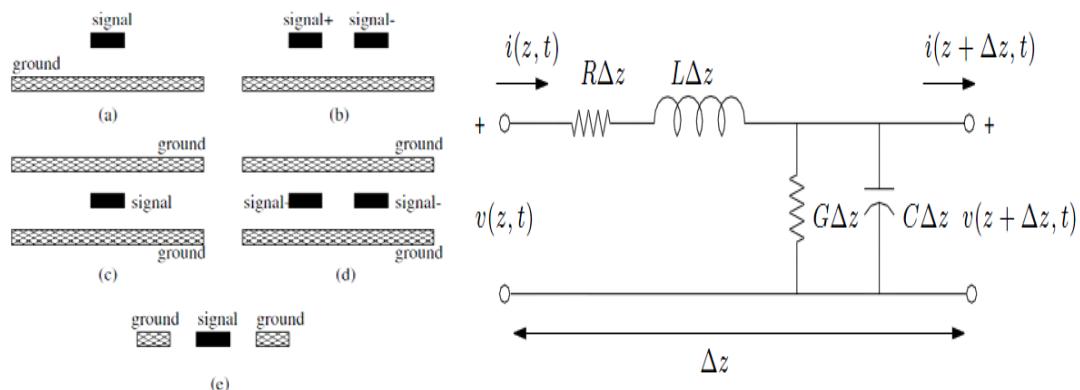

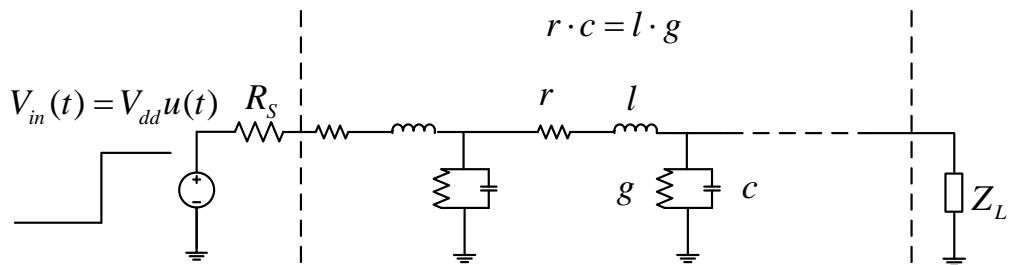

### 4.3.1 用于栅极扫描线的无畸变传输线

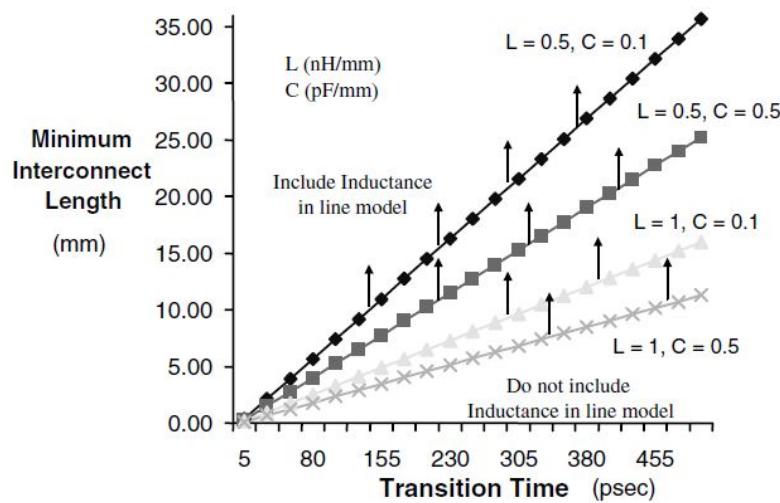

如前所述，对于栅极扫描线，可以近似为如图 4-4 所示的结构，在这种结构中，只有电阻  $R_g$  和电容  $C_g$  被考虑了，扫描线被近似为 RC 互连线，其上信号具有较大畸变，增加了信号的延迟，破坏了信号的完整性。考虑到 4.2 节的分析，如图 4-12 所示，当信号的转变时间越小，互连线的长度越长，线上电感、电容越大时，互连线上的电感越需要考虑<sup>[88]</sup>。对于用作栅极扫描线的互连线，其长度非常长，若按照 4-14 中  $L=1nH/mm$ ,  $C=0.5pF/mm$  的曲线进行计算，对于长为 50cm 的互连线，当转变时间小于大约 25ns 时就必须考虑电感，可见对于大尺寸高分辨率显示，考虑栅极扫描线上的电感是必要的。在本节中，本论文将视扫描线为传输线，调优线上电感，同时插入电导，使其构成无畸变传输线，减少信号延迟并增加信号完整性。

对于高分辨率面板，若分辨率为  $M \times N$ ，则一行像素将有  $3M$  个，若  $M > 1000$ ，则一行像素超过 3000 个，本节中一行的像素个数取为 1000 个，这足可以使栅极扫描线近似看成分布系统。在实际中，线上分布参数将随频率变化，因而在每一个频率上满足 Heaviside 条件是不可能的，正如上一节所述，对于高频分量，其衰减和速度不与频率直接相关，而对于低频分量，衰减和速度则与频率直接相关，

故在调优和构造满足 Heaviside 条件的分布参数时，可以采用低频时的参数值，即采用“match at DC”方法<sup>[112-115]</sup>，其对信号完整性的改善情况与不考虑 rclg 随频率变化的情况类似<sup>[113]</sup>，在本节和下一节中，分布参数 rclg 被近似的认为不随频率变化<sup>[96][117]-[120]</sup>，本论文将在这一理想情况下分析以无畸变传输线做栅极扫描线对信号完整性的改善情况。根据文献中报道的寄生电阻和电容的数量级，我们选取一个像素线上电阻和电容<sup>[95]-[98]</sup>为  $r=0.425\Omega$ ,  $c=0.11\text{pF}$ , 一个像素线上电感<sup>[112]-[115]</sup>为  $l=0.0405\text{nH}$ 。

图 4-12 需要考虑线上电感的条件<sup>[88]</sup>

图 4-13 用无畸变传输线做栅极扫描线示意图

若要构成无畸变传输线，则需要插入的电导值为  $g= rc/l$ ，但对于一般的 rcl 值， $g$  值会变得过大以至于最末像素上接收到的波形衰减的过于严重，此时，我们可以考虑增大线上电感  $l$  来减小插入的电导  $g$  值。实际上，早在 100 年以前，

Heaviside 就曾提出以添加电感的方式来改善横跨大西洋电缆上信号的完整性。若我们能将一个像素线上电感提升至  $10\text{nH}$ , 则需插入的电导为  $4.675\mu\text{S}$ 。这样, 用无畸变传输线做成的栅极扫描线如图 4-13 所示, 其中每一个像素的电阻  $r$ , 电感  $l$ , 电容  $c$ , 和插入的电导  $g$  满足 Heaviside 条件。由于缓冲器的电容对信号的影响较小, 为简化, 在以后的分析中一律不考虑。

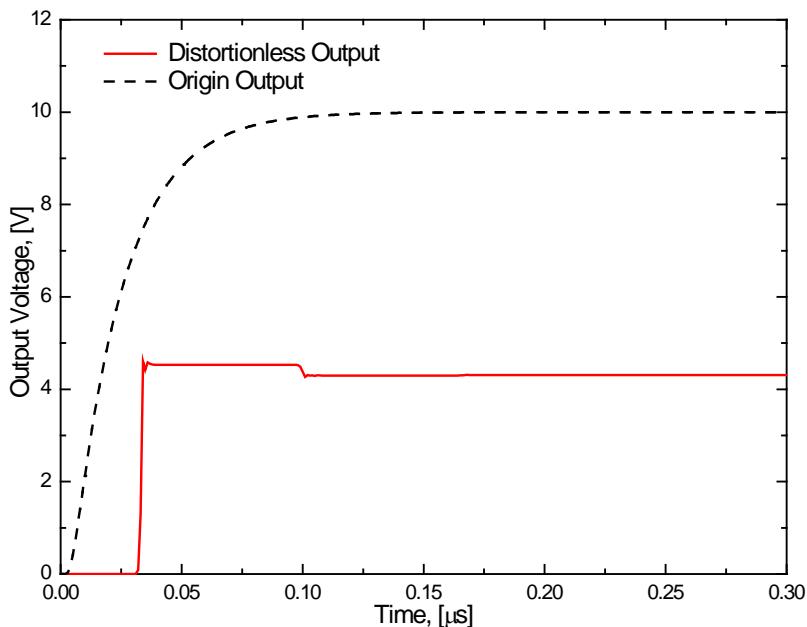

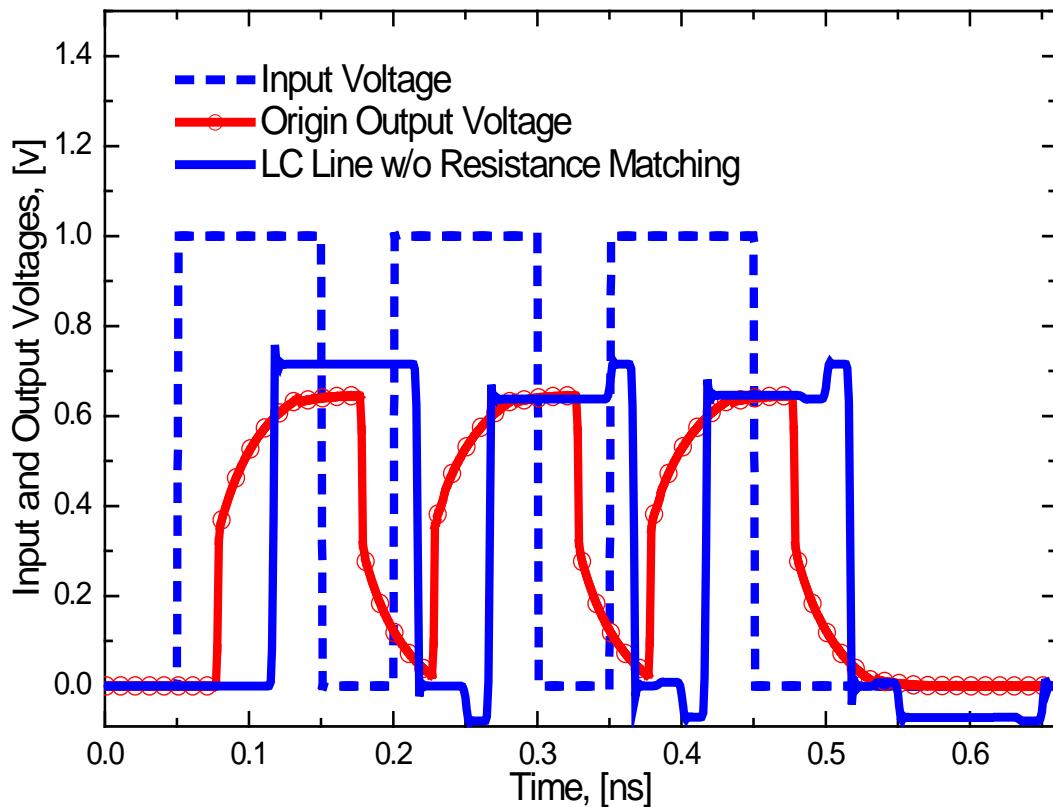

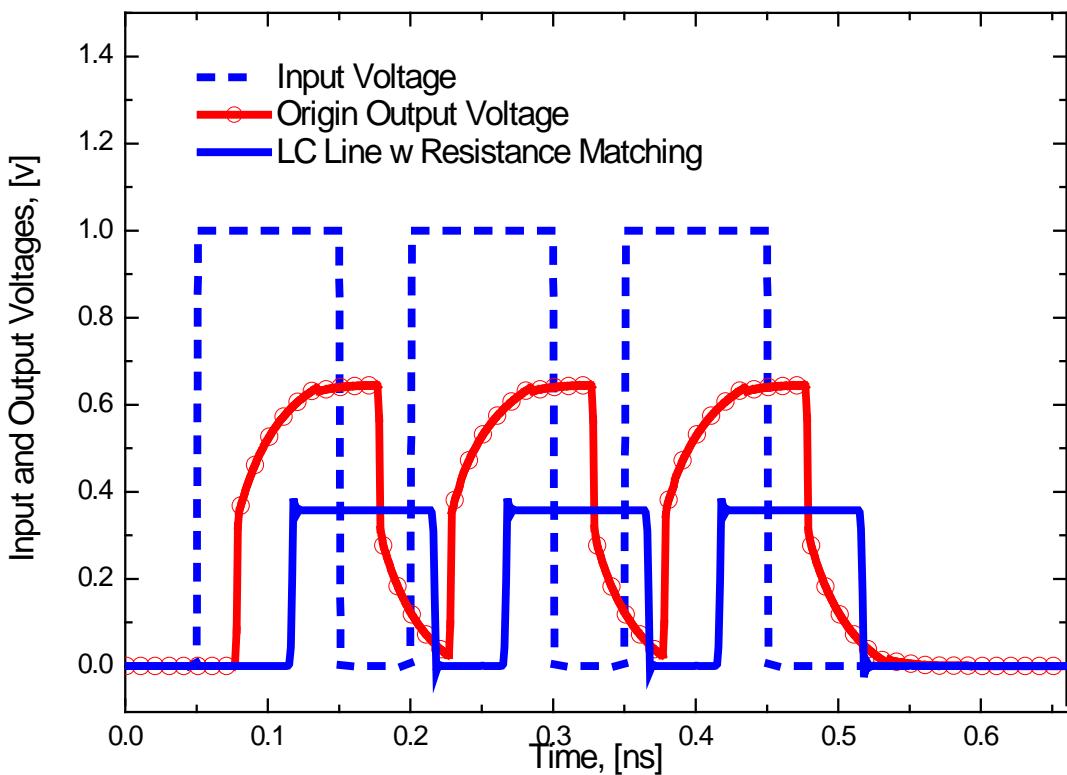

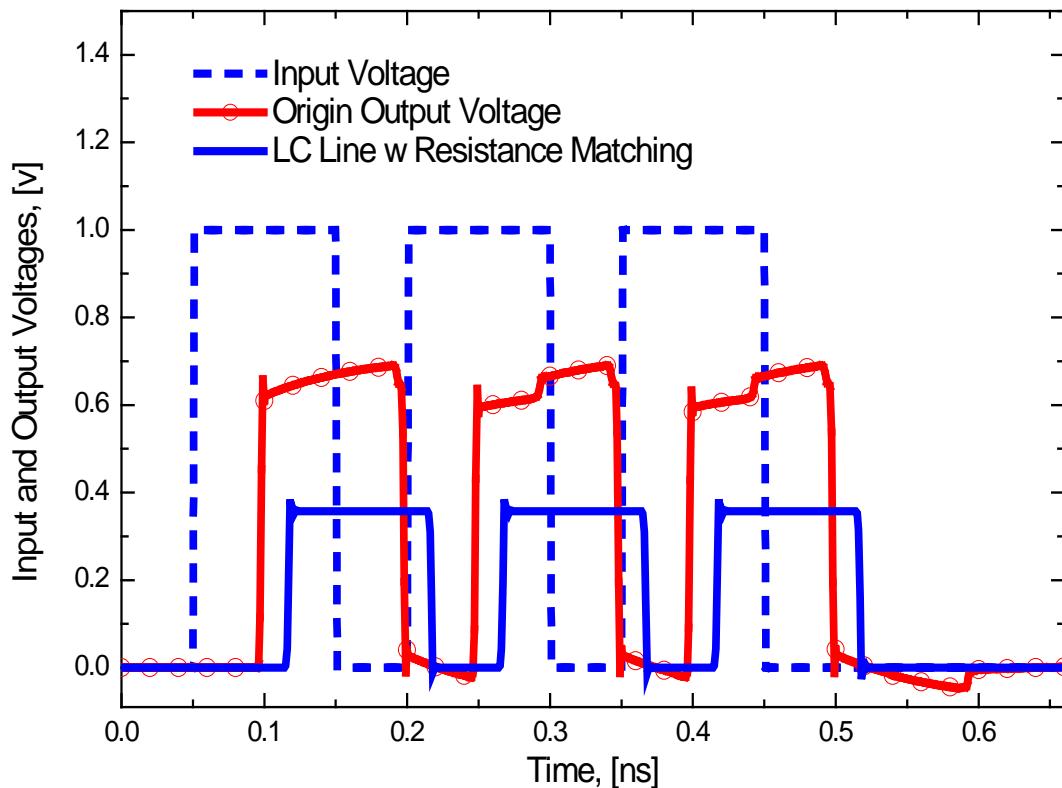

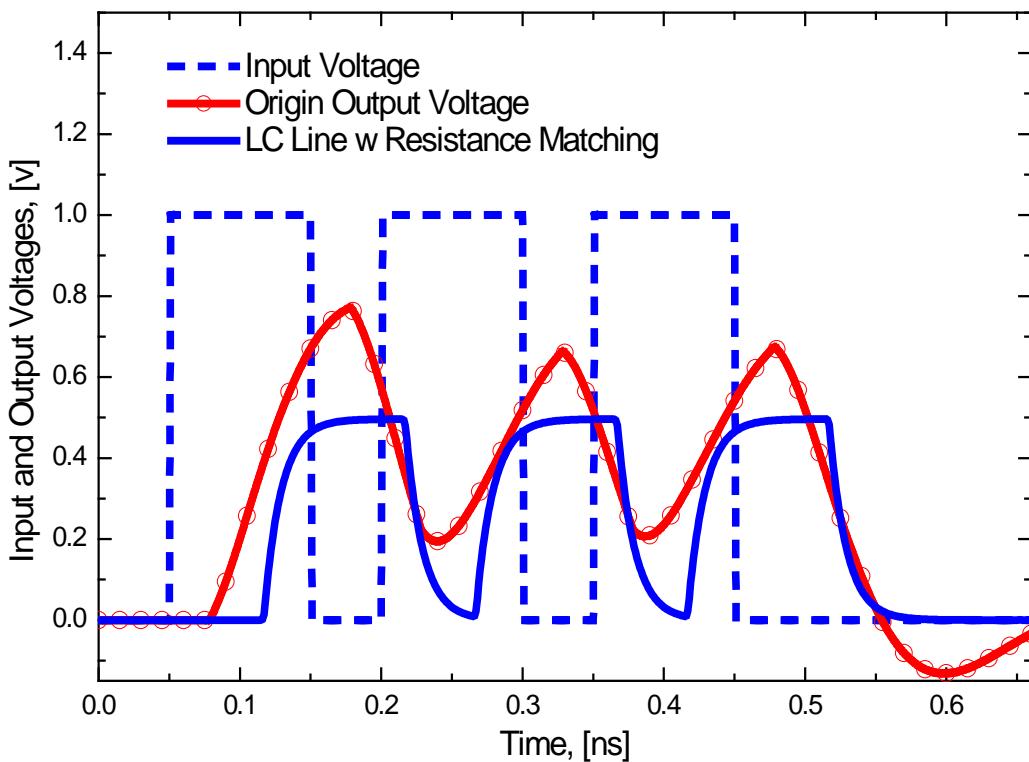

### 4.3.2 无畸变传输线用作栅极扫描线对信号完整性的改善

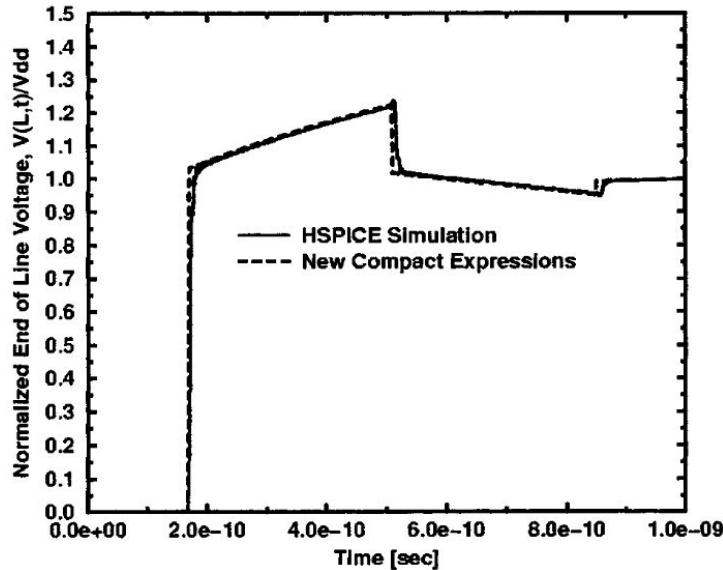

图 4-14 栅极扫描线原输出波形以及调优电感并插入电导后的输出波形

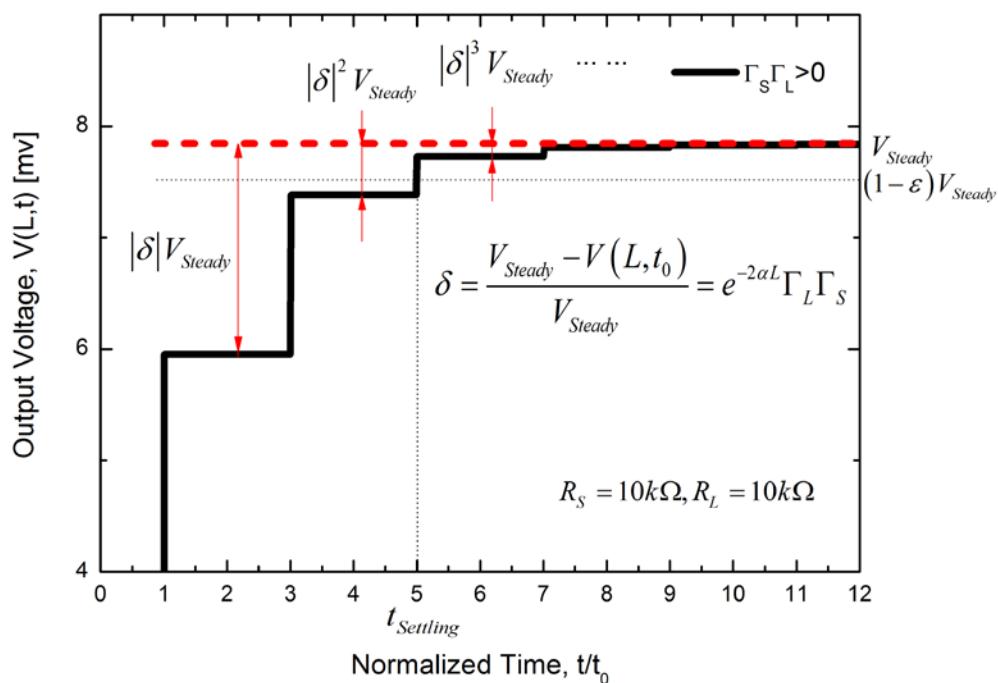

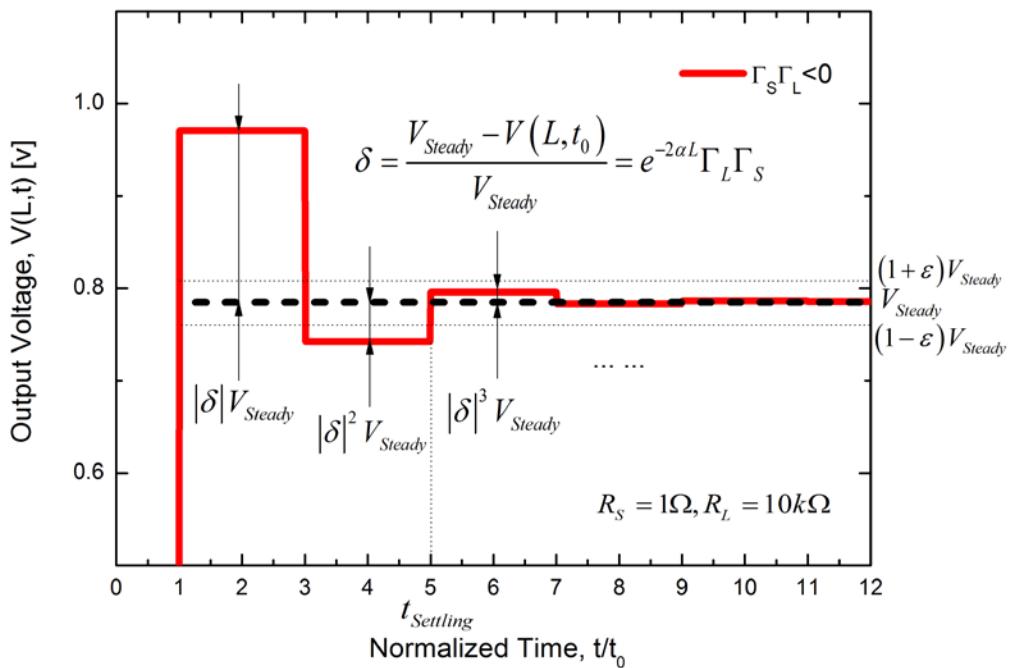

当输入电阻  $R_s=23.54\Omega$ , 负载  $Z_L$  为开路, 阶跃输入电压为  $V_{dd}=10\text{V}$  时, 图 4-14 显示了在最末像素栅极扫描线原输出波形以及调优电感并插入电导后的无畸变输出波形。可以明显看到, 在加入电导并调优电感以后, 正如无畸变传输线理论预测的那样, 相比于原输出波形, 无畸变传输线输出波形几乎在飞行时间  $0.034\mu\text{s}$  处立即跳变到与稳定值相差 5% 的范围内, 波形近似为阶跃电压, 而原输出波形则相对要有很大的延迟, 要达到稳定值的 95% 需要  $0.069\mu\text{s}$ , 为无畸变传输线的两倍, 由此可见输出信号的延迟确实减小了, 信号完整性增强了。和理论分析得到的结论一致, 无畸变传输线会导致信号振幅的下降, 但经过电感调优以后的振幅值约为原振幅的一半, 可以直接应用或易被传感器感知。

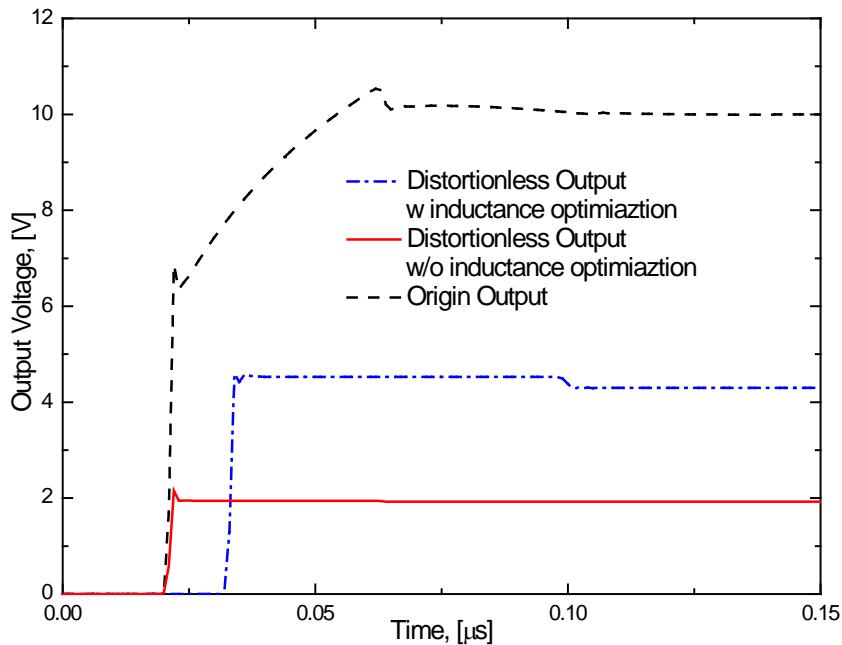

此外, 若原输出线材料和结构可使其上电感值足够大时, 也可以直接插入电

导而不必再调优电感，对于  $r=0.425\Omega$ ,  $c=0.11\text{pF}$ ,  $l=4.05\text{nH}$  的原栅极扫描传输线，图 4-15 示出了原输出信号，插入电导后 ( $g=rc/l$ )，同时调节电感(提升至  $10\text{nH}$ )和电导后的输出信号，可见，仅插入电导后的信号完整性同样大大增强了，而以增加飞跃时间为代价的电感调优方案则增大了稳定电压的值，同时信号的延迟和原信号相比还是大大减小了。

图 4-15 原输出信号、插入电导后与同时调节电感和电导后的输出信号比较