IEEE EDL九月刊发表我实验室超薄栅介质TFT研究成果

国际微电子领域权威期刊IEEE Electron Device Letters 今年第九期刊登了我实验室在超薄栅介质方面的研究成果“Self-Aligned Top-Gate Amorphous InGaZnO TFTs With Plasma Enhanced Chemical Vapor Deposited Sub-10 nm SiO2 Gate Dielectric for Low-Voltage Applications”。

(文章链接:https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=8777103)

近年来,非晶InGaZnO(a-IGZO)薄膜晶体管(TFT)因为具有较高的载流子迁移率、良好的大面积均匀性、对可见光透明、较低的工艺温度等优点,被认为是有源矩阵显示的下一代背板技术。除了在显示领域外,a-IGZO TFT还在大面积微电子和先进集成电路等领域中展示了巨大的应用潜力,例如高密度CMOS图像传感器、BEOL晶体管、3维堆叠存储器等。为了适应这些新兴应用,亟需降低a-IGZO TFT的工作电压及功耗。增加栅极电容是降低其工作电压的一个有效途径,即减小栅介质层的厚度或使用高κ材料作为栅介质。迄今为止,各种各样的高k介质已经得到了广泛的研究,如Y2O3、HfO2、ZrO2、Ta2O5、HoTiO3、HfLaO和Al2O3等。然而,高κ材料的带隙通常很小,相应的band offset也会随着k值的增加而减小。此外,高κ栅介质还可能在介质内部或介质与a-IGZO的界面处引入高密度缺陷态。另一方面,高κ介质的非常规制备方法不可避免地增加了制备工艺的复杂性和生产成本。

鉴于与a-IGZO良好的界面匹配和生产工艺兼容性,我们认为通过减薄等离子体增强化学气相沉积(PECVD)制备的SiO2的厚度可能是降低a-IGZO TFT工作电压及功耗的优选解决方案。然而,目前关于超薄PECVD SiO2对a-IGZO TFT的可行性的研究尚未报道。这篇文章研究了传统PECVD工艺生长的超薄 SiO2薄膜的电学性质并成功制备了具有8.62nm PECVD SiO2栅介质的自对准顶栅a-IGZO TFT。

该论文的第一作者为硕士生张羽晴同学,论文共同作者还有杨欢、彭昊、曹允开、秦禄东同学和张盛东老师。此项研究是在深圳TFT与先进显示重点实验室完成,受NSFC (61574003和61774010)以及深圳科技计划(GGFW20170728163447038 和JCYJ20180504165449640)等项目的支持。

Fig. 1. (a) Cross-sectional schematic and (b) major processing steps of the SATG a-IGZO TFT, respectively, and (c) TEM images of the TFT at interfaces revealing that the thickness of the PECVD SiO2 gate dielectric is 8.62 nm.

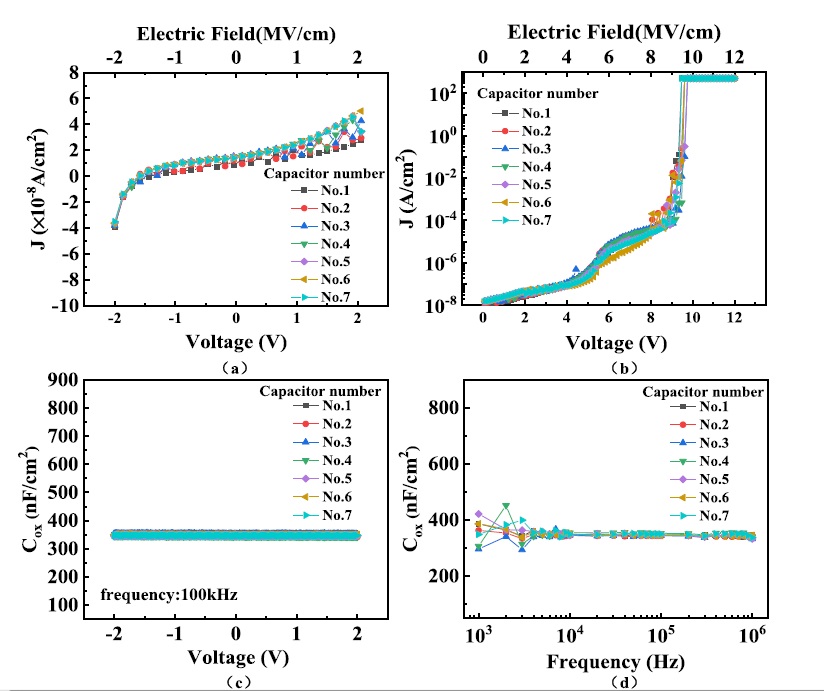

Fig. 2. Electrical properties of Mo/SiO2/Mo capacitors with 8.62 nm PECVD SiO2 dielectric. (a) Leakage current characteristics, (b) breakdown characteristics, (c) C-V, and (d) C-F characteristic. The capacitor area is 140 µm × 140 µm.

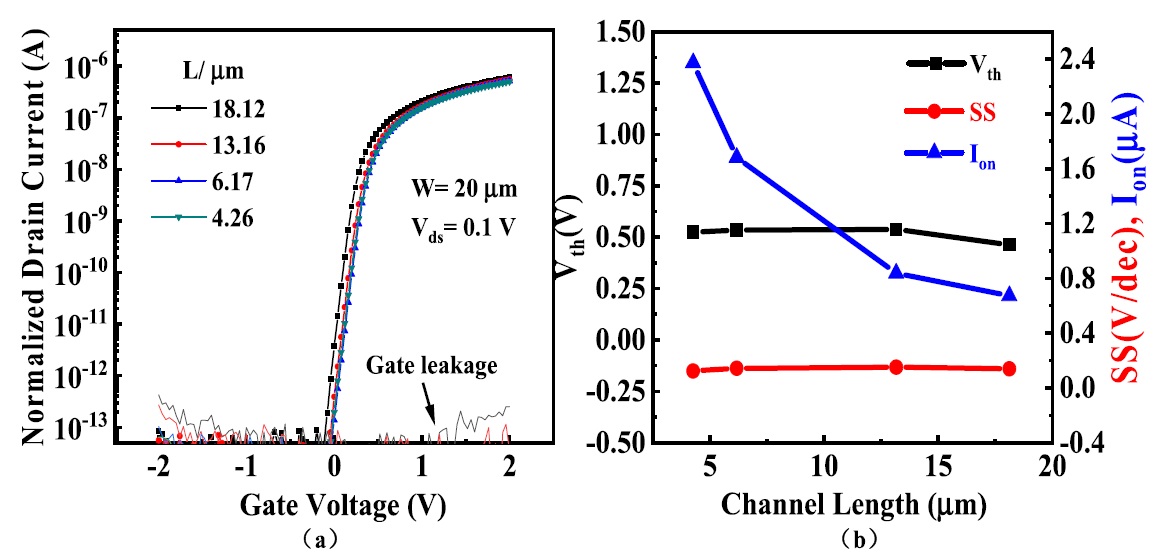

Fig. 3. (a) W/L normalized transfer characteristics at various channel lengths of the SATG a-IGZO TFTs with 8.62 nm PECVD SiO2 gate dielectric. (b) The dependence of the Vth, SS, and Ion on the channel length of the TFTs.

(供稿:张羽晴)