IEEE JEDS三月刊发实验室底栅同质结型a-IGZO TFT技术研究成果

近期, IEEE Journal of the Electron Devices Society刊登了我实验室在a-IGZO TFT制备技术方面的研究论文: ” Homo-Junction Bottom-Gate Amorphous In-Ga-Zn-O TFTs With Metal-Induced Source/Drain Regions”,(论文链接: https://ieeexplore.ieee.org/document/8494735)

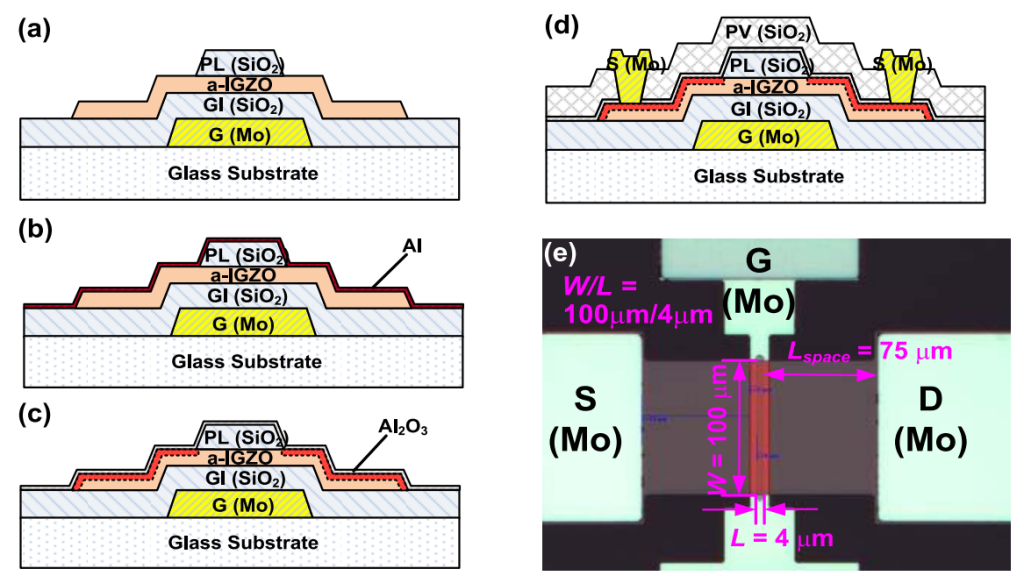

对于氧化物TFT而言,较常采用的器件结构是底栅交错结构,而底栅交错结构又分为ESL型和BCE型。但是这两种制备工艺各自都存在着难以解决的技术难点,其中ESL技术存在制备工艺复杂、器件寄生电容大以及沟道长度难以缩小的问题。而BCE工艺中背沟道刻蚀技术一直难以突破。因此,为了化解当前BCE和ESL技术的难题,人们提出了同质结型器件制备技术,目前,实现同质结结构的关键技术之一就是对源漏区进行掺杂,具体包括Ar或H2等离子体处理、通过生长SiNx钝化层的方式向源漏区进行H掺杂等方法。但是这些方法存在热稳定性差等问题,使器件特性难以控制。

本文提出了制备底栅同质结型a-IGZO TFT器件的新工艺。通过在a-IGZO上覆盖一层薄的Al薄膜然后进行热处理,就能够获得具有良好热稳定性的低阻a-IGZO源漏区,由此制得的a-IGZO TFT具有很低的源漏寄生电阻,甚至比传统ES工艺制得器件的源漏寄生电阻更低。此外,热氧化形成的Al2O3薄膜能够阻挡H扩散和水分子进入,因此有效增强了器件的钝化效果。与传统采用Ar等离子体处理的器件相比,采用Al反应制备的器件具有高电学性能、高热稳定性且不受外界环境气氛影响的优势。

该论文的第一作者为邵阳博士后,共同作者还包括周晓梁博士,杨欢,常宝柱,梁婷,王漪老师以及张盛东老师。在此向他们表示祝贺!该研究在深圳薄膜晶体管与先进显示重点实验室(Shenzhen TFT and Advanced Display Lab)完成,并且受NSFC(61574003)和NSFC(61774010)项目的资助。