Recently, prof. Zhang Min and Wen Jinyuan, the corresponding author and the first author of our research group, published the paper entitled “high speed low power rail to rail buffer using dynamic current feedback for OLED source driver applications” on Analog Integrated Circuits and Signal Processing.

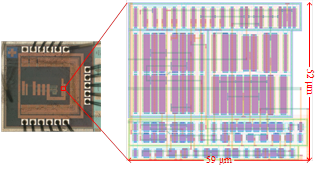

In this work, we propose a rail-to-rail output buffer with low static-power and high speed for OLED display applications. To guarantee low static power consumption, low tail-current is designed in the buffer’s first stage and the output stage is cut off in the static operation. To improve the transient response, dynamic-current-bias technique is used, and it also improves the system stability by pushing away the non-dominant pole. Meanwhile, we balance the large-signal slew-rate and system stability with dual-output buffer structure. Placing compensation resistor across the dual outputs creates zero for suitable phase margin, while the real output still behaves with low ON resistance and keeps high slew rate. The proposed design has been verified by a 0.18 μm 1.8 V/5 V CMOS process, which shows that the buffer only draws 2.8 μA static current. Under a 1 nF capacitance load and a 5 V power supply, the buffer achieves 1.18 μs settling time, which is only 41% of the single-output-stage structure with the same chip size (52 μm×59 μm).